ILA(Integrated Logic Analyzer)는 디지털 회로의 디버깅과 분석을 위해 사용되는 도구이다. FPGA(Flexible Programmable Gate Array) 디자인에서 유용하다. ILA는 디지털 회로의 내부 신호를 모니터링하고 분석하는 데 도움이 되며, 디버깅 시간을 단축하고 회로의 동작을 이해하는데 도움이 된다.

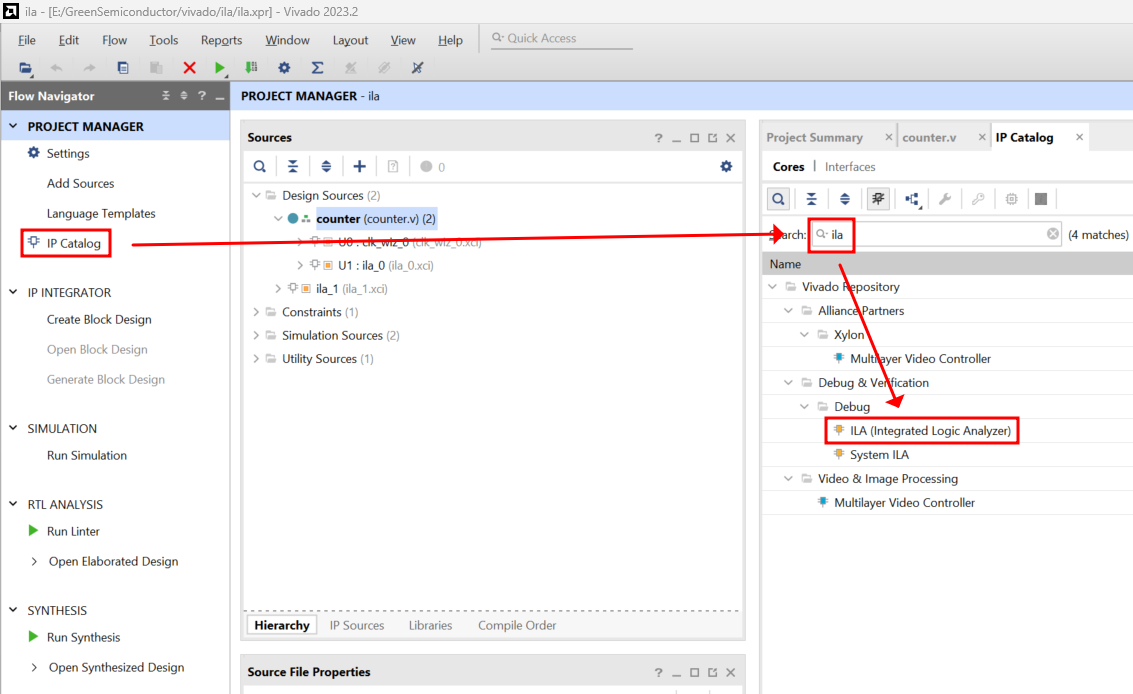

좌측 IP Catalog를 클릭하여 검색창에 ila를 검색한다.

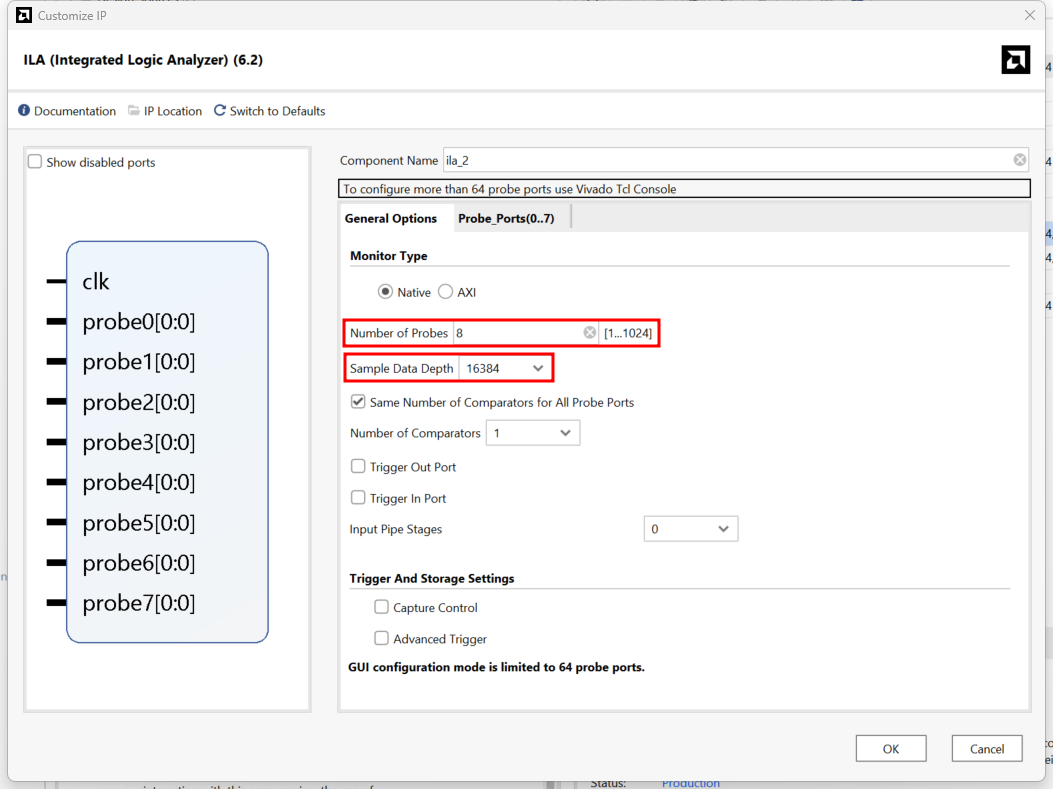

Number of probes는 ILA로 캡처하려는 시그널의 수를 지정하는 항목이다. 이 값은 ILA에서 감시하고 분석할 수 있는 시그널의 개수를 결정한다.

일반적으로 디버깅할 시그널의 수가 많을수록 문제 해결이 더욱 쉬워지지만, FPGA 디바이스의 리소스가 한정되어 있기 때문에 최적의 수를 지정해야 한다.

Sample Data Depth는 각각의 프로브에 대해 ILA가 저장하는 샘플 데이터의 깊이를 지정하는 항목이다. 이 값은 ILA가 시그널의 값을 캡처하고 저장하는 데 사용하는 내부 버퍼의 크기를 결정한다.

만약 Sample Data Depth가 1024로 설정되어 있다면, ILA는 각 시그널에 대해 최대 1024개의 샘플을 저장할 수 있다.

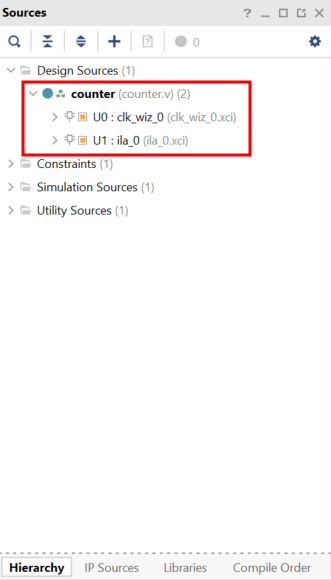

위와 같이 ila를 생성하게 되면, (이전에 생성한 clock wizard와 같이) verilog에 의해 자동으로 ila 모듈이 생성된다.

counter.v

module counter(clk,rst,count);

input clk,rst;

output reg [7:0] count;

wire clk_5;

clk_wiz_0 U0(.clk_in1(clk), .clk_out1(clk_5));

ila_0 U1(.clk(clk),

.probe0(count[7]),

.probe1(count[6]),

.probe2(count[5]),

.probe3(count[4]),

.probe4(count[3]),

.probe5(count[2]),

.probe6(count[1]),

.probe7(count[0])

);

always@(posedge clk_5 or negedge rst)

begin

if(!rst)

count=0;

else

count=count+1;

end

endmodule위는 간단한 counter code를 작성하여 ila 모듈을 인스턴스화 하여 작성한 코드에 해당한다.

counter의 각 자리 수를 샘플링하여 신호를 측정하려는 코드에 해당한다.

합성 및 bitstream을 통해 디지털 회로를 구성하고 ila를 통해 counter의 각 자리의 신호를 분석하게 되면, LSB를 기준으로 MSB 방향으로 하나씩 커질 수록 신호 주기는 2배씩 커지는 것을 확인할 수 있다.(이진수는 각 자리수가 2배이기 때문에 0, 1 신호 주기가 2배씩 차이나기 때문이다.)

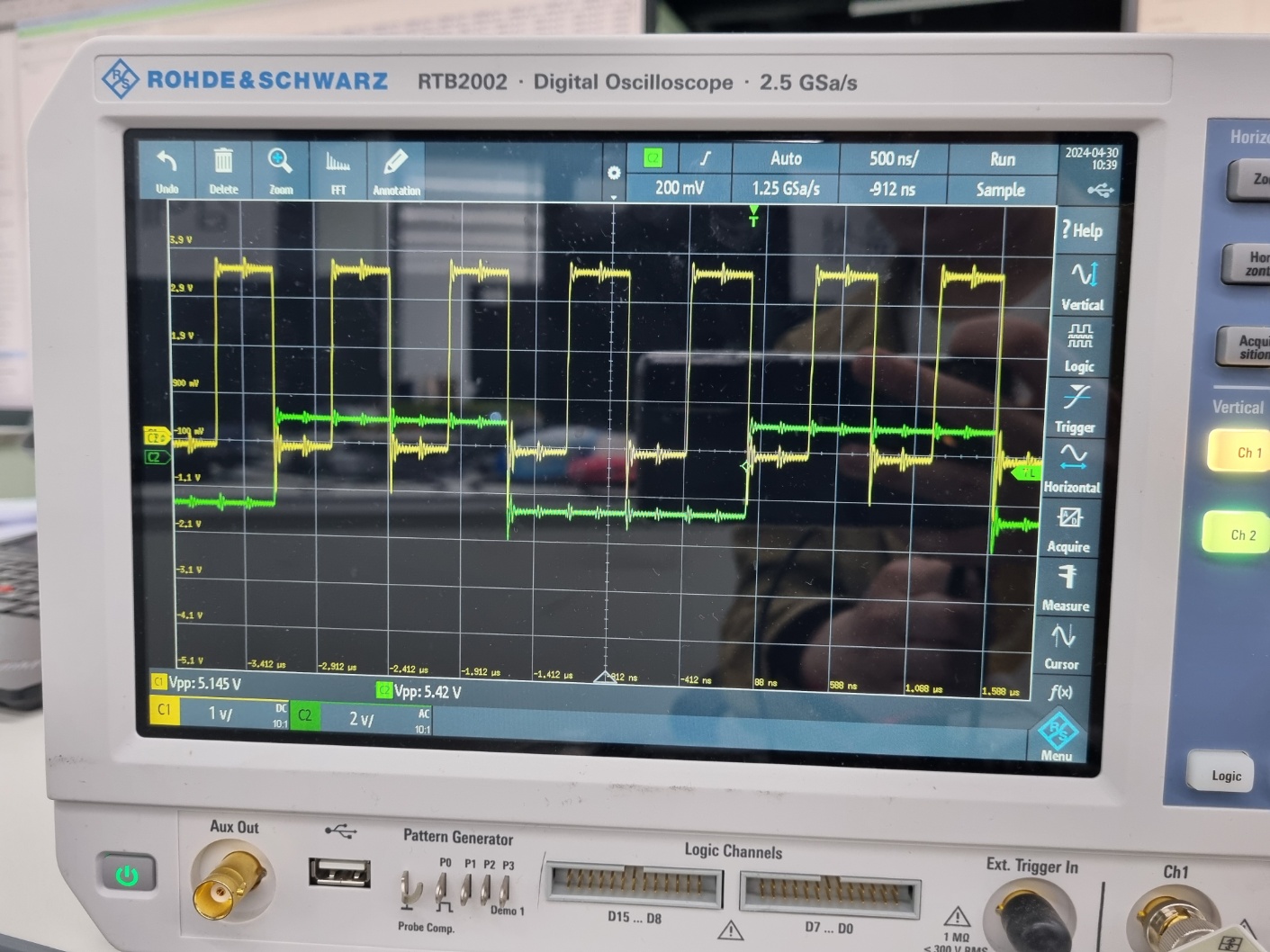

아래 사진은 오실로스코프를 통해 ila를 통해 출력된 신호와 실제 신호가 일치하는지 확인한 사진이다.

counter의 LSB를 기준으로 두번째 세번째 자리와 비교한 값이다.

counter의 LSB와 두번째 자리의 주기 차이가 2배가 나는 것을 확인할 수 있다.

counter의 LSB와 세번째가 4배 차이나는 것을 확인할 수 있다.

'Semiconductor > FPGA' 카테고리의 다른 글

| FPGA - STM32 UART 이용한 DC Motor 제어 및 신호 확인 (0) | 2024.07.30 |

|---|---|

| FPGA - SPI 통신을 이용한 DC Motor 제어하기 (0) | 2024.07.15 |

| FPGA - CHARACTER LCD에 문자 입력하기 (0) | 2024.06.18 |

| FPGA - FPGA를 이용한 DC 모터 구동 (0) | 2024.06.11 |

| FPGA - 7-Segment Count Up (0~9999) / FPGA (0) | 2024.06.02 |