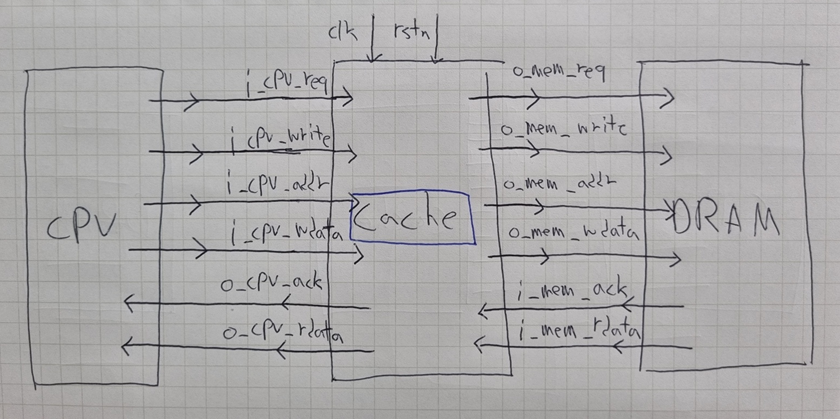

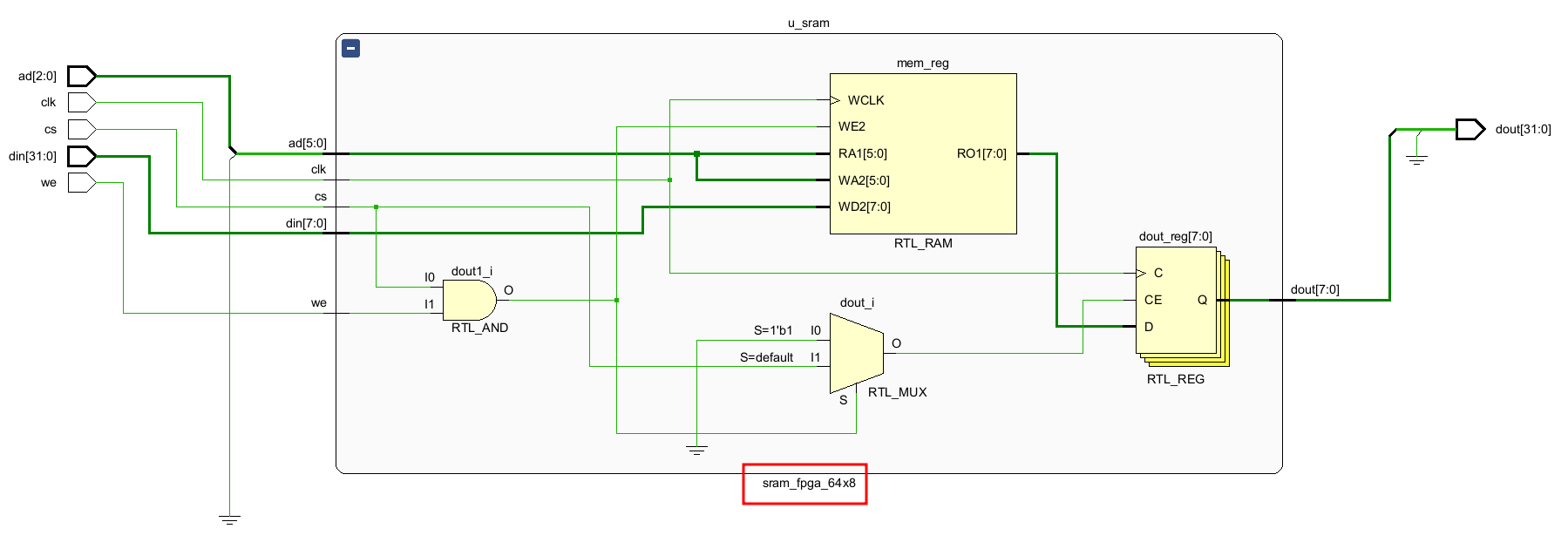

■ CACHE 구조 https://insoobaik.tistory.com/661 Cache 구조 및 동작 원리보호되어 있는 글입니다. 내용을 보시려면 비밀번호를 입력하세요.insoobaik.tistory.comCACHE에 대한 내용은 위 글을 참조하길 바랍니다.■ Block Diagram■ 설계 조건 및 입/출력 Port - 설계 조건 Block size = 4BMemory size = 256B (64 Blocks)Cache size = 16B (4 Sets)Write-backreq & ack handshakingOne req at a time - 입/출력 Port - clk : 동기화를 위한 Clock 신호를 전달하기 위한 Port- rstn : 비동기 reset을 위한 Port - i_cpu_req..