시프트 레지스터는 한 플롭의 출력 핀 q가 다음 플롭의 데이터 입력핀(d)에 연결되는 일련의 플립플롭이다. 모든 플롭은 동일한 클럭에서 작동하기 때문에 시프트 레지스터에 저장된 비트 배열은 한 위치만큼 이동한다.

ex) 5bit 오른쪽 시프트 레지스터의 초기 값이 10110이고 시프트 레지스터에 대한 입력이 0에 묶여 있으면 다음 패턴은 01011이 되고 다음 패턴은 00101이 된다.

설계

시프트 레지스터 설계에는 5개의 입력과 1개의 n비트 출력이 있다.

parameter MSB를 사용하여 매개변수화를 통해 시프트 레지스터의 폭을 나타낸다.

주요 기능

1. input d(design) 핀을 통해 활성화, 비활성화 할 수 있다.

2. input dir을 통해 왼쪽, 오른쪽으로 이동할 수 있다.

3. input rstn이 0의 값을 가지면 시프트 레지스터가 재설정되고 출력은 0이 된다.

4. 시프트 레지스터의 입력 데이터 값은 d pin으로 제어 가능하다.

shift_reg.v

`timescale 1ns / 1ps

module shift_reg #(parameter MSB = 8) (

input d, input clk, input en, input dir, input rstn,

output reg [MSB-1:0] out

);

always @(posedge clk)

if (!rstn)

out <= 0;

else begin

if(en)

case(dir)

0 : out <= {out[MSB-2:0], d};

1 : out <= {d, out[MSB-1:1]};

endcase

else

out <= out;

end

endmodule

tb_sr.v

`timescale 1ns / 1ps

module tb_sr();

parameter MSB = 16;

reg data;

reg clk;

reg en;

reg dir;

reg rstn;

wire [MSB-1:0] out;

shift_reg #(MSB) sr0(.d(data), .clk(clk), .en(en), .dir(dir), .rstn(rstn), .out(out));

always #10 clk = ~clk;

initial begin

clk <= 0;

en <= 0;

dir <= 0;

rstn <= 0;

data <= 'b1;

end

initial begin

rstn <= 0;

#20 rstn <= 1;

en <= 1;

repeat (7) @ (posedge clk)

data <= ~data;

#10 dir <= 1;

repeat (7) @ (posedge clk)

data <= ~data;

repeat (7) @ (posedge clk);

$finish;

end

initial

$monitor ("rstn=%0b data=%b, dir=%0b, out=%b", rstn, data, en, dir, out);

endmodule

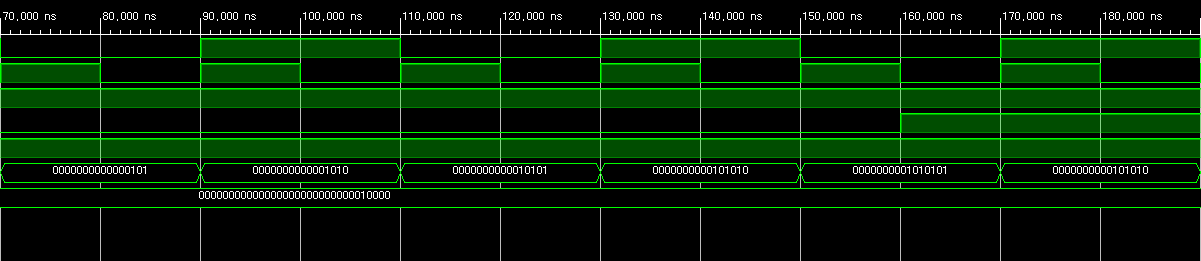

아래 시뮬레이션을 보게 되면 첫번째 그림의 경우 dir이 0일 때 좌측 시프트가 적용되기 때문에 좌측 시프트로 데이터가 이동하는 것을 확인 할 수 있다.

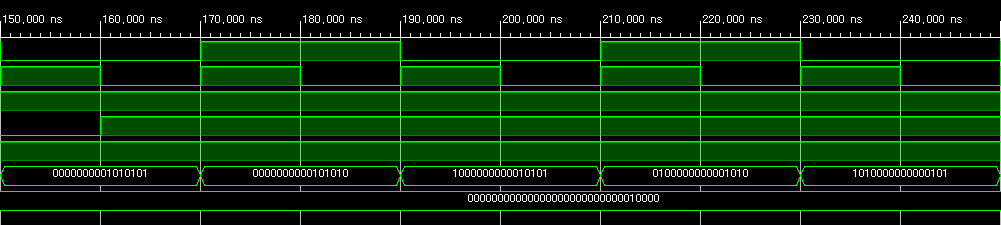

두번째 시뮬레이션의 경우 dir이 1이기 때문에 우측 시프트가 적용되어 데이터가 우측 시프트로 이동하는 것을 확인 할 수 있다.

728x90

'Semiconductor > RTL, Simulation' 카테고리의 다른 글

| RTL - SRAM (`ifdef를 이용한 FPGA, ASIC 코드 분리) (0) | 2024.08.06 |

|---|---|

| RTL - SPI (Master, Slave, FSM) (2) FSM, MASTER, SLAVE & SLVAE 활용 (0) | 2024.06.02 |

| RTL - SPI (Master, Slave, FSM) (1) FSM, SLAVE (0) | 2024.06.02 |

| RTL - Xcelium, Verilog를 이용한 CPU RISC 구조 설계 (0) | 2024.06.02 |

| Xcelium - (Verilog 파일 전송 및 Xcelium 실행) (2) | 2024.04.03 |