(기본적인 Linux 사용법은 알고 있다고 가정한다.)

Xcelium 기본 명령어

csh : C Shell의 약어

xrun : 시뮬레이션을 실행하는 데 사용되며, 다양한 옵션을 설정하여 시뮬레이션 동작을 제어할 수 있다.

-access +rwc : 디자인 파일에 대한 액세스 권한을 설정한다. +rwc는 읽기, 쓰기 및 변경이 가능한 엑세스를 의미한다.

-gui : GUI를 열도록 한다. 시뮬레이션 결과 및 디버깅 정보를 시각적으로 확인할 수 있다.

Verilog를 이용하여 코드를 작성한다.

Verilog Code

nor3_bitop.v

module nor3_bitop (

input [2:0] a,

output out_nor3

);

assign out_nor3 = ~(a[2] | a[1] | a[0]);

endmodule

nor3_gp.v

module nor3_gp (

input [2:0] a,

output out_nor3

);

nor (out_nor3, a[2], a[1], a[0]);

endmodule

nor3_if.v

module nor3_if (

input [2:0] a,

output out_nor3

);

reg out_nor3;

always @(a) begin

if(a == 3'b000) out_nor3 = 1'b1;

else out_nor3 = 1'b0;

end

endmodule

nor3_redop.v

module nor3_redop (

input [2:0] a,

output out_nor3

);

assign out_nor3 = ~|a;

endmodule시뮬레이션을 통해 확인 할 testbench 코드를 작성한다.

Verilog Testbench Code

tb_nor3.v

module tb_nor3();

reg [2:0] a;

integer i;

nor3_bitop U0 (a, out_nor3_bitop);

nor3_redop U1 (a, out_nor3_redop);

nor3_gp U2 (a, out_nor3_gp);

nor3_if U3 (a, out_nor3_if);

initial begin

for (i=0; i<=7; i=i+1) begin

a = i;

#10;

end

#20 $finish;

end

endmoduleXcelium을 통한 시뮬레이션 실행을 위한 스크립트 파일 생성 (그냥 명령어를 통해 실행해도 무방하다.)

nor_src.f (스크립트 파일)

nor3_bitop.v

nor3_redop.v

nor3_gp.v

nor3_if.v

tb_nor3.v

-access

+rwc

-gui

시뮬레이션 실행 코드

xrun -f [파일명]

또는 명령이를 직접 입력하는 방식을 사용

csh

xrun [파일명1] [파일명2]... -access +rwc -guiXcelium 실행 및 시뮬레이션 확인

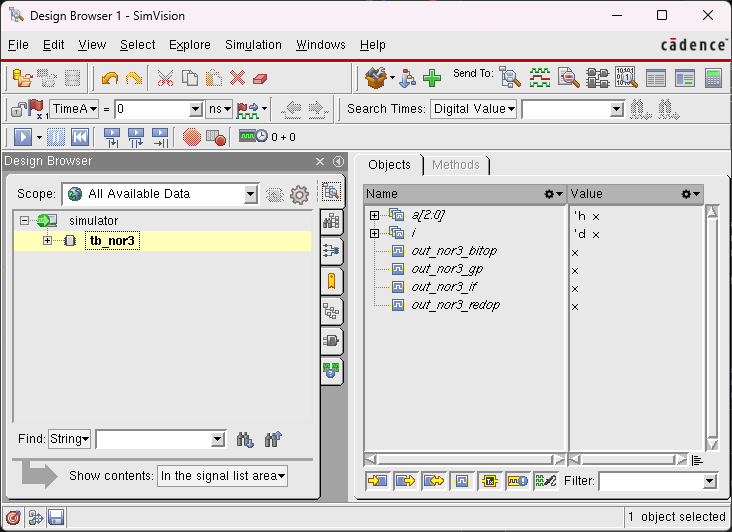

코드에 이상이 없다면 Xcelium이 동작하여 위와 같은 화면을 띄운다.

시뮬레이션을 통해 보고 싶은 변수를 클릭하고 시뮬레이션을 실행시킨다.

시뮬레이션이 실행되고 시작버튼을 누르게 되면 시뮬레이션이 실행되는 것을 확인할 수 있다.

728x90

'Semiconductor > RTL, Simulation' 카테고리의 다른 글

| RTL - SRAM (`ifdef를 이용한 FPGA, ASIC 코드 분리) (0) | 2024.08.06 |

|---|---|

| RTL - SPI (Master, Slave, FSM) (2) FSM, MASTER, SLAVE & SLVAE 활용 (0) | 2024.06.02 |

| RTL - SPI (Master, Slave, FSM) (1) FSM, SLAVE (0) | 2024.06.02 |

| RTL - Xcelium, Verilog를 이용한 CPU RISC 구조 설계 (0) | 2024.06.02 |

| RTL - n비트 양방향 시프트 레지스터 (0) | 2024.03.30 |