SPI는 주변 장치들과의 통신을 위한 시리얼 통신 프로토콜을 구현하는데 사용된다.

SPI는 다음과 같은 구성 요소로 구성된다.

1. Master와 Slave : SPI 통신은 하나의 마스터와 하나 이상의 슬레이브로 구성된다. 마스터는 통신을 제어하고 슬레이브 간에 데이터를 전송한다.

2. Serial 데이터 전송 : SPI는 시리얼 방식으로 데이터를 전송한다. 이것은 비트 단위로 직렬로 전송되며, 일반적으로 데이터는 MSB 또는 LSB부터 전송된다.

3. 시간 동기화 : SPI는 시간 동기화 방식을 사용하여 통신한다. 마스터는 클럭 신호를 생성하여 통신 속도를 제어하며, 데이터는 클럭 신호의 edge에 따라 전송된다.

4. 전송 모드 : SPI는 여러 전송 모드를 지원한다. 주로 사용되는 모드에는 CPOL 및 CPHA가 있다. 이러한 모드는 클럭 신호의 시작 상태 및 데이터 샘플링 시기를 정의한다.

5. 통신 프로토콜 : SPI는 간단하고 유연한 프로토콜을 사용한다. 주로 데이터 전송을 위해 MOSI 및 MISO 라인을 사용하며, 추가적으로 SS 및 SCK 라인이 사용된다.

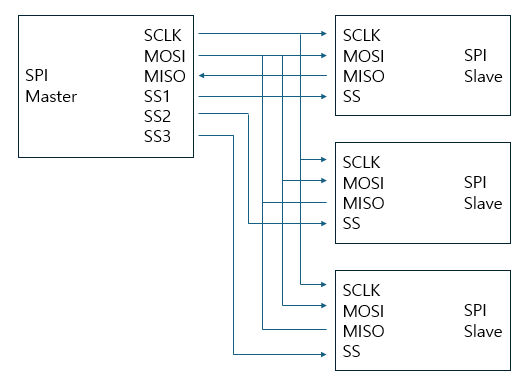

SPI는 기본적으로 Master와 Slave로 구성된다.

위 그림과 같이 하나의 Master가 여러 Slave에게 통신 제어 신호를 보내게 되면 그 신호에 맞게 Slave들이 데이터를 송수신하게된다.

통신에 사용되는 대표적인 신호에는 MOSI, MISO, SS, SCK가 있고, Mode 설정을 위한 CPHA, CPOL이 있다.

SCK (Serial Clock) : SCK는 시리얼 클럭 신호를 나타낸다. 이 클럭 신호는 마스터 장치에서 생성되며, 데이터를 전송하는 동안 데이터의 시간적인 흐름을 동기화한다.

MOSI (Master Out Slave In) : MOSI는 마스터에서 슬레이브로 데이터를 전송하는 데 사용되는 핀이다. 마스터가 데이터를 출력하고 슬레이브가 데이터를 입력한다.

MISO (Master In Slave Out) : MISO는 슬레이브에서 마스터로 데이터를 전송하는 데 사용되는 핀이다. 슬레이브가 데이터를 출력하고 마스터가 데이터를 입력한다.

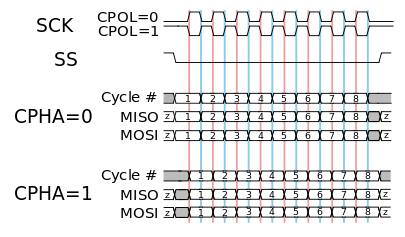

CPOL (Clock Polarity) : CPOL은 클럭 신호의 극성을 나타낸다. CPOL이 0이면 LOW 상태가 비활성화 상태, CPOL이 1이면 HIGH 상태가 비활성화 상태에 해당하게 된다.

CPHA (Clock Phase) : CPHA는 클럭 신호의 페이즈를 나타낸다. CPHA가 0이면 클럭 신호가 비활성화 상태에서 활성 상태로 변경될 때 샘플링을 진행하고, CPHA가 1이면 클럭 신호가 활성 상태에서 비활성화 상태로 변경될 때 샘플링을 진행한다.

SS (Slave Select) : SS는 슬레이브 장치를 선택하기 위한 신호다. 마스터는 특정 슬레이브 장치와 통신하기 위해 해당 SS 핀을 활성화한다.

SPI Mode

| Mode | CPOL | CPHA |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

SPI 동작 Mode에는 4가지가 있다.

1. Mode 0

CPOL이 0이면 Low 신호가 비활성화 상태에 해당하며, CPHA이 0이면 비활성화 상태에서 활성 상태가 될 때 샘플링한다.

위 그림과 같이 Low에서 High가 될 때 샘플링을 진행한다.

2. Mode 1

CPOL이 0이면 Low 신호가 비활성화 상태에 해당하며, CPHA이 1이면 활성 상태에서 비활성화 상태가 될 때 샘플링한다.

위 그림과 같이 High에서 Low가 될 때 샘플링을 진행한다.

3. Mode 2

CPOL이 1이면 High 신호가 비활성화 상태에 해당하며, CPHA이 0이면 활성 상태에서 비활성 상태가 될 때 샘플링한다.

위 그림과 같이 High에서 Low가 될 때 샘플링을 진행한다.

4. Mode 3

CPOL이 1이면 High 신호가 비활성화 상태에 해당하며, CPHA이 1이면 비활성화 상태에서 활성 상태가 될 때 샘플링을 진행한다.

위 그림과 같이 Low에서 High가 될 때 샘플링을 진행한다.

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| 통신 프로토콜 UART 동작 원리 (0) | 2024.07.16 |

|---|---|

| FPGA - LUT(Look-Up Table) (0) | 2024.07.12 |

| 디지털 논리 회로 - 기본 상식 (트랜지스터, Chip) (0) | 2024.04.05 |

| 반도체 기본 - N, P형 반도체 / 다이오드, 트렌지스터 / P,N,C MOS (0) | 2024.04.03 |

| Verilog - 기본 문법 정리 (0) | 2024.03.30 |