FPGA 내부의 디지털 회로 구성에 있어 가장 기본이 되는 요소는 LUT와 FF(Filp-Flop)이다. 이 중 LUT에 대해 알아보겠다.

- LUT(Look-Up Table)

LUT는 입력값에 따라 미리 정의된 출력값을 반환하는 테이블 형태의 데이터 구조다.

디지털 회로에서 복잡한 논리나 연산을 간단한 테이블 조회로 처리할 수 있게 해준다.

기본적으로 FPGA는 4-INPUT LUT를 사용하는데 (5-INPUT, 6-INPUT도 존재한다.) 4개의 input 조합할 수 있는 모든 Bool 함수 구현이 가능하다.

y = (a & b) | c위 로직은 아래와 같아 AND, OR 게이트를 사용해서 다음과 같이 구성할 수 있다.

| a | b | c | d |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

위 로직에 대한 진리표를 확인해보면 위와 같이 8개의 입력 조합을 확인할 수 있다.

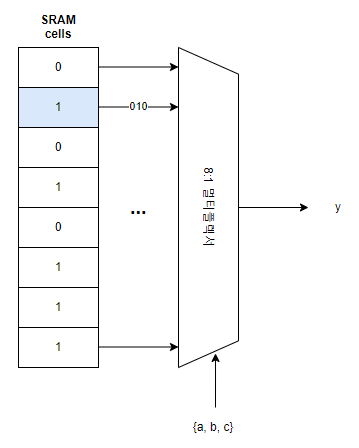

LUT는 아래 그림과 같이 입력 신호에 맞춰 8개의 출력 y를 SRAM cell에 저장한다.

LUT가 아래와 같이 정의되면 입력 신호에 따라 cell에서 값을 검색하여 하나의 값을 Mux를 통해 반환할 수 있게된다.

자일링스 울트라 스케일 아키텍쳐는 6-input LUT를 사용한다. 즉 64개의 출력 값이 미리 SRAM에 초기화되어 있고 6비트 입력을 받는 Mux가 존재한다.

아래 그림과 같이 툴을 사용하여 합성(Synthesis)하게 되면 코드를 분석하여 적절하게 LUT를 배치하게 된다. 따라서 FPGA에 얼마나 복잡한 로직을 넣을 수 있는지는 합성기의 성능이 좌우한다.

728x90

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| 디지털 논리 회로 정리 - 1 (기본) (0) | 2024.07.22 |

|---|---|

| 통신 프로토콜 UART 동작 원리 (0) | 2024.07.16 |

| 디지털 논리 회로 - 기본 상식 (트랜지스터, Chip) (0) | 2024.04.05 |

| 반도체 기본 - N, P형 반도체 / 다이오드, 트렌지스터 / P,N,C MOS (0) | 2024.04.03 |

| SPI - Serial Peripheral Interface 통신 (0) | 2024.04.01 |