UART란

UART(Universal asynchronous receiver/transmitter)는 병렬 데이터의 형태를 직렬 방식으로 전환하여 데이터를 전송하는 컴퓨터 하드웨어의 일종이다.

통신 데이터는 메모리 또는 레지스터에 들어 있어 이것을 차례대로 읽어 직렬화 하여 통신한다. 최대 8비트가 기본 단위이다.

UART는 일반적으로 컴퓨터나 주변 기기의 일종으로 병렬 데이터를 직렬화 하여 통신하는 개별 집적 회로다.

비동기 통신이므로 동기 신호가 전달되지 않는다. 따라서 수신 쪽에서 동기신호를 찾아내어 데이터의 시작과 끝을 시잔적으로 알아 처리할 수 있도록 약속되어 있다.

| 비트수 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 시작 비트(Start bit) | 5~8 데이터 비트 | 패리티 비트(Parity bit) | 종료 비트(Stop bit(s)) | ||||||||

| Start | Data 0 | Data 1 | Data 2 | Data 3 | Data 4 | Data 5 | Data 6 | Data 7 | Parity | Stop | |

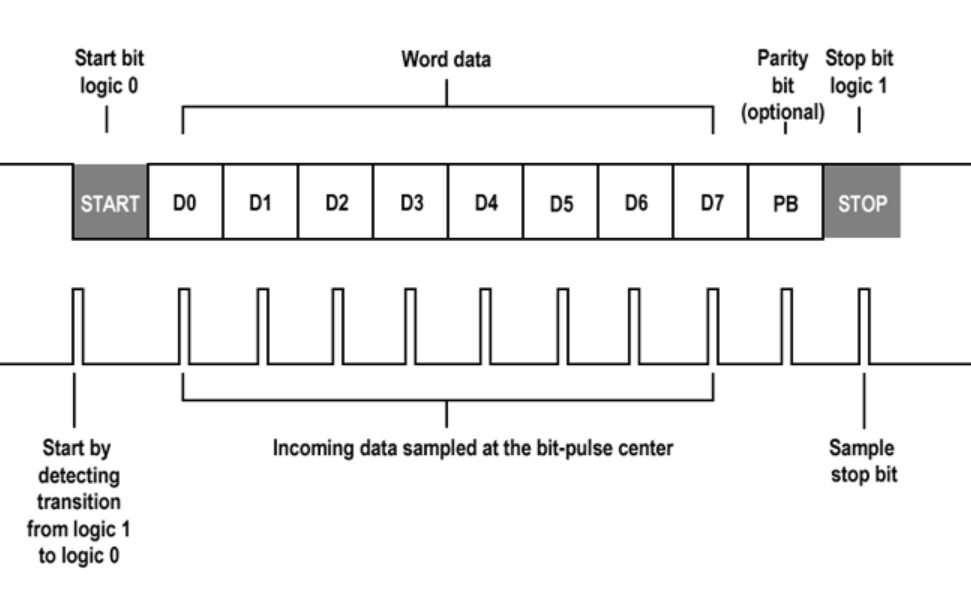

- 시작 비트 : 통신의 시작을 의미하며 한 비트 시간 길이 만큼 유지한다.

- 데이터 비트 : 5~8비트의 데이터 전송을 한다. 몇 비트를 사용할 것인지는 해당 레지스터 설정에 따라 결정된다.

- 패리티 비트 : 오류 검증을 하기 위한 패리티 값을 생성하여 송신하고 수신쪽에 오류를 판단한다. (사용x, 홀수, 짝수) 패리티 등의 세가지 옵션으로 해당 레지스터 설정에 따라 선택할 수 있다. 사용x을 선택하면 패리티 비트가 삭제된다.

- 끝 비트 : 통신 종료를 알린다. 세가지의 정해진 비트 만큼 유지해야 한다. 1, 1.5, 2비트로 해당 레지스터 설정에 따라 결정된다.

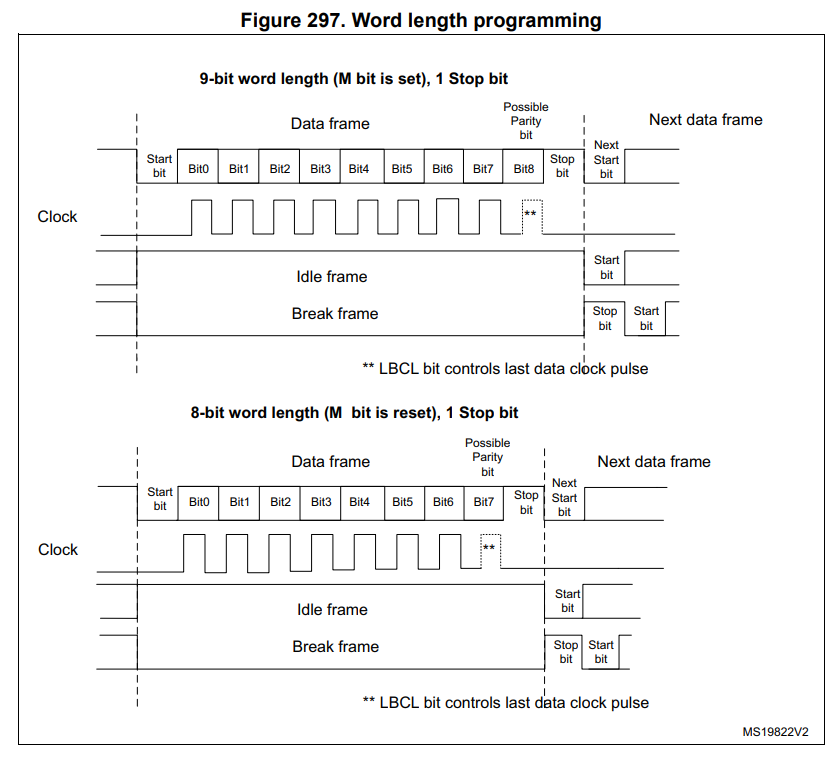

UART 통신의 기본 Start, Stop, Parity, Data가 존재하는 것은 공통적이지만 위와 같이 STM32F429 Manual을 보게 되면 STM32의 경우 Start, Stop bit가 정의되어 있고, Data frame에 Parity bit를 포함시키는 식으로 동작되는 것을 확인할 수 있다.

동작 방식

수신 UART는 시작 비트를 감지함으로써 Baud Rate(보 레이트)라는 특정 주파수를 통해 들어오는 데이터를 읽기 시작한다.

Baud Rate는 초당 전송 비트수를 뜻하여 9600 Baud Rate라고 하면 1초에 9600비트를 전송할 수 있다는 것을 뜻하며, 1/9600초에 1비트씩 전송 가능한 속도를 가지게 된다.

수신, 송신 측의 Baud Rate는 일치해야 하며 Baud Rate가 다를 경우 전송된 데이터가 달라질 수 있다. (Baud Rate가 정확히 일치하지 않아도 오차 허용 범위 내에선 데이터가 정상적으로 전달될 수 있다.)

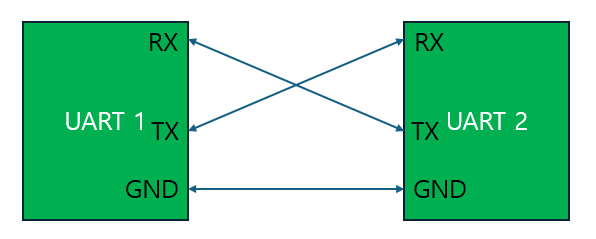

또한 2개의 UART는 동일한 데이터 패킷 구조를 송, 수신하도록 구성되어야 한다.

송, 수신 방법

1. Start Bit

UART 전송을 위한 물리적인 와이어는 데이터를 전송하지 않을 때는 High Level로 유지된다. 데이터 전송이 시작되면, 송신 UART는 High Level에서 Low Level로 한 클럭 사이클 동안 변경한다.

수신 UART는 Low Level로 변경되면, 설정한 Baud Rate 주파수로 Rx 핀을 통해 흘러 들어오는 데이터 비트르르 읽기 시작한다.

2. Data Frame

데이터 프레임의 크기는 5~8비트를 가질 수 있고, Parity 비트를 사용하지 않으면, 데이터 크기를 최대 9비트까지 사용할 수 있다.

3. Parity Bit

수신 UART에서 송신 UART가 전송한 데이터 프레임이 전송과정에서 변경되었는지 확인한다. 데이터는 외부 여러 요인과 서로 다른 Baud Rate에 의해서 변경될 수 있다.

Parity Bit가 0이면 데이터 프레임 비트는 짝수, Parity Bit가 1이면 데이터 프레임 비트는 홀수여야 한다.

4. Stop Bit

송신 UART는 1~2비트 크기의 정지 비트를 가지며, 물리적인 와이어를 Low Level에서 High Level로 변경하는 방식으로 수신 UART에게 알린다.

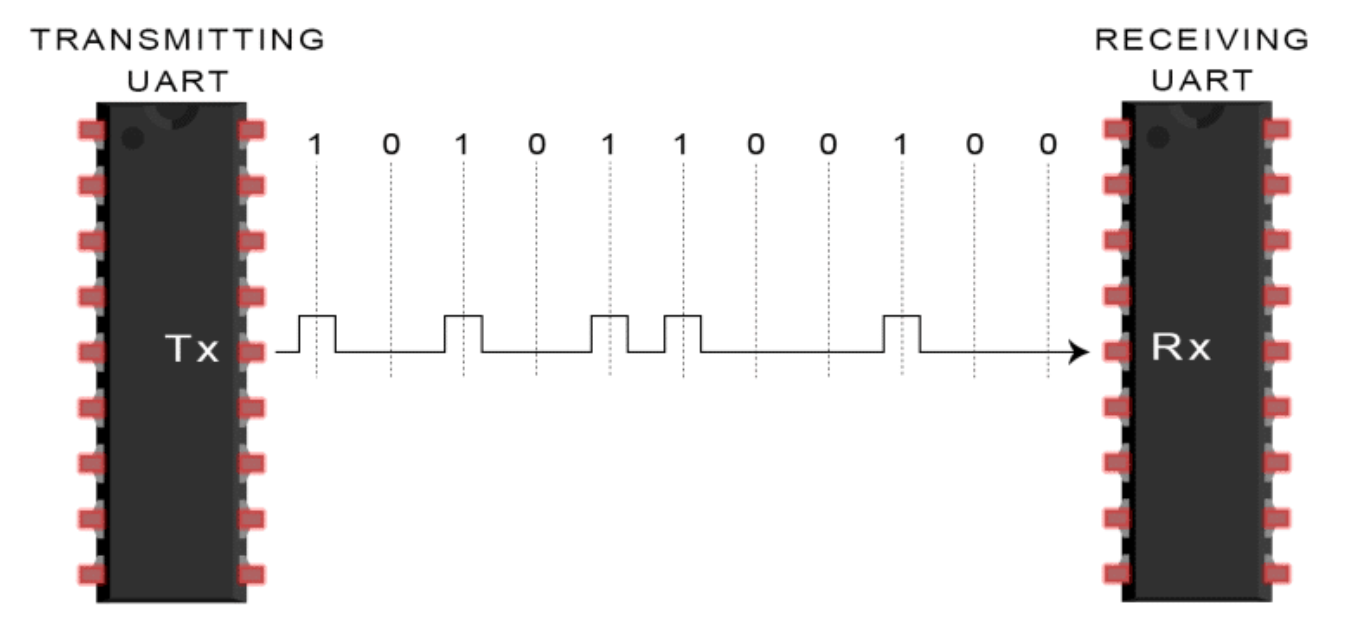

위 그림에서

1. 처음 0 으로 변경될 때 Start Bit에 의해 데이터가 전송되는 것을 확인한다.

2. 0100 1101 8비트의 데이터가 전달된다.

3. 이후 Parity Bit 0이 전달되여 데이터 비트가 짝수여야 함을 알 수 있다.

4. Parity Bit 0이후 1 High Level의 신호가 전달되면 Stop Bit에 의해 전송이 종료되었음을 알 수 있다.

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| 디지털 논리 회로 정리 - 2 (논리 회로) (0) | 2024.07.23 |

|---|---|

| 디지털 논리 회로 정리 - 1 (기본) (0) | 2024.07.22 |

| FPGA - LUT(Look-Up Table) (0) | 2024.07.12 |

| 디지털 논리 회로 - 기본 상식 (트랜지스터, Chip) (0) | 2024.04.05 |

| 반도체 기본 - N, P형 반도체 / 다이오드, 트렌지스터 / P,N,C MOS (0) | 2024.04.03 |