- AND Gate는 신호를 masking 하는데 사용 가능하다.

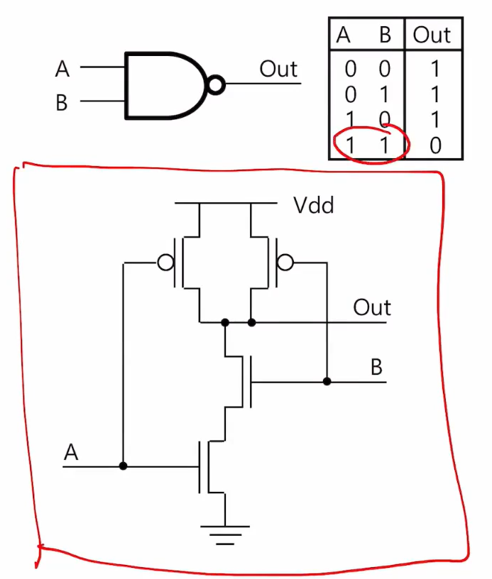

- NAND는 AND + INVERTER를 합쳐서 표현할 수 있다.

- NAND 게이트는 Negative-OR 게이트와 동일하다.

- 3입력 XOR 게이트는 입력 신호 1의 개수가 홀수일 때 1을 출력한다.

- XNOR 게이트 등가 게이트 구조

좌측 XNOR 게이트와 우측 논리 게이트 회로는 등가 회로에 해당한다.

- 고정된 기능의 IC Gates

1. CMOS(Complementary Metal-Oxide Semiconductor)

Field-Effect Transistor(FET) 사용

- 낮은 전력 소모

2. TTL(Transistor-Transistor Logic)

- Bipolar 트랜지스터 사용

3. ECL(Emitter-Coupled Logic)

- 빠른 속도

- 많은 전력 소모

| 특성 | BJT | FET |

| 제어 방식 | 전류 제어 | 전압 제어 |

| 입력 임피던스 | 낮음 | 높음 |

| 전력 소모 | 상대적으로 높음 | 낮음 |

| 속도 | 빠름 | 매우 빠름 |

| 주요 응용 | 전류 증폭, 스위칭 | 전압 증폭, 고속 스위칭, 아날로그 신호 처리 |

| 주요 유형 | NPN, PNP | JFET, MOSFET |

* 임피던스는 회로 전체에 대한 복합적인 저항 성분을 뜻한다.

- Propagation Delay

Propagation delay time : 전달(전파) 지연 시간

- 신호가 입력되어 출력될 때까지의 시간

- 게이트의 동작속도를 나타낸다.

- Fan-in & Fan-out

- Fan-in : 1개의 게이트에 입력할 수 있는 개수

- Fan-out : 1개의 게이트의 출력이 구동 가능한 최대 게이트 수

- Pull-up & Pull-down

- Pull-up : 전원 쪽으로 연결할 때

- Pull-down : 접지쪽으로 연결할 때

모든 논리 게이트에 대해서 입력 신호에 대해서 아무런 신호를 전달하지 않으면 안된다.

위와 같이 Pull-up이나 Pull-down을 통해 일정 신호를 전달해줘야 한다.

부울대수의 기본 법칙

- 교환 법칙

A + B = B + A

A*B = B*A

- 결합 법칙

(A+B)+C = A+(B+C)

(A*B)*C = A*(B*C)

- 분배 법칙

A*(B+C) = A*B + A*C

A+(B*C) = (A+B)*(A+C)부울대수에서 AND(*)의 OR(+)의 연산 우선순위는 동일하기 때문에 A+(B*C) =(A+B)*(A+C)로 분배가 가능하다.

- 드모르간 법칙

nA*nB = nA+nB

nA+nB = nA*nB* NAND와 Negative-OR의 결과 값과 NOR와 Negative-AND의 결과 값이 동일한 것을 통해 위 드모르간 법칙을 증명할 수 있다.

- 흡수 법칙

A+A*B = A

A*(A+B) = A

- 그 외

A + 0 = A

A + 1 = 1

A + A = A

A + nA = 1

A * 0 = 0

A * 1 = A

A * A = A

A * nA = 0

nnA = A위 사항들은 진리표를 그려보면 해당 결과가 나오는 것을 알 수 있다.

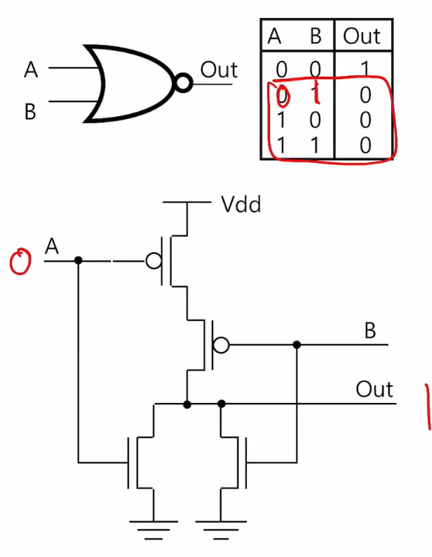

- NAND 게이트가 AND 게이트보다 차지하는 공간이 작고, NAND 게이트가 NOR 게이트보다 차지하는 공간이 작다.

* NAND 게이트의 경우 4개의 트랜지스터를 사용하지만 AND 게이트의 경우 최소 6개의 트랜지스터를 사용하기 때문이다.

- SOP(Sum of Products) 곱의 합 / POS (Products of Sum) 합의 곱

곱의 합에서는 내부 곱이 1이 되는 값을 찾고, 합의 곱에서는 내부 합이 0이 되는 값을 찾는다.

SOP는 AND-OR 로직으로 구현된다.

모든 부울 수식은 SOP로 변환 가능하다.

- 카르노 맵

카르노맵은 논리 변수들이 모든 가능한 조합을 나타내는 표이며, 각 셀은 논리식에서 결과값을 나타낸다.

1. 논리식 단순화

2. 불변성 분석

3. 에러 발견

SOP 카르노 맵

1. 진리표에 값을 넣듯이 카르노 맵에 1을 넣는다.

2. 최소개의 직사각형으로 1을 묶으며 직사각형은 1,2,4,8,16의 크기를 가져야하고 각 직사각형의 크기는 최대로 크게 한다.

3. 그룹화된 직사각형마다 SOP 항을 만든다.

4. SOP 항들을 합으로 묶어서 출력을 표현한다.

X = AB(bar) + AB| A / B | 0 | 1 |

| 0 | ||

| 1 | 1 | 1 |

위 식의 경우 카르노맵을 위와 같이 작성할 수 있으며 결과적으로 X = A이란 값을 얻게 된다.

카르노 맵에서 돈케어(x)는 그룹화를 해도되고 안해도 상관없다.

- 그레이 코드란 인접한 셀들이 한개의 비트만 다른 것을 의미한다.

| AB/C | 0 | 1 |

| 00 | ||

| 01 | ||

| 11 | ||

| 10 |

00, 01, 11, 10의 경우 한개의 비트씩 달라지는 것을 확인할 수 있다.

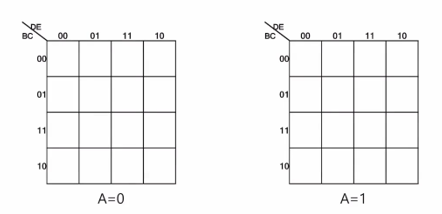

- 5변수 카르노 맵의 경우 16개짜리 카르노 맵 2개를 사용하며, A, B, C, D, E의 경우 하나는 A=0 / A=1일 때 두 개의 카르노 맵을 아래 위로 연결한다.

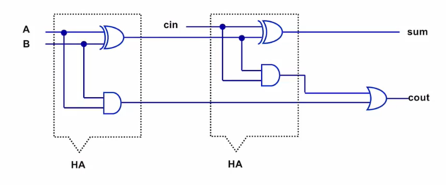

- 전가산기

- 전자는 고전위에서 저전위로 흐른다.

- 정공은 저전위에서 고전위로 이동한다.

- 전류의 흐름은 전자의 이동방향과 반대로 흐른다.

- NMOS는 전자의 이동에 의해 전류가 흐르고, PMOS는 정공의 이동에 의해 전류가 흐른다.

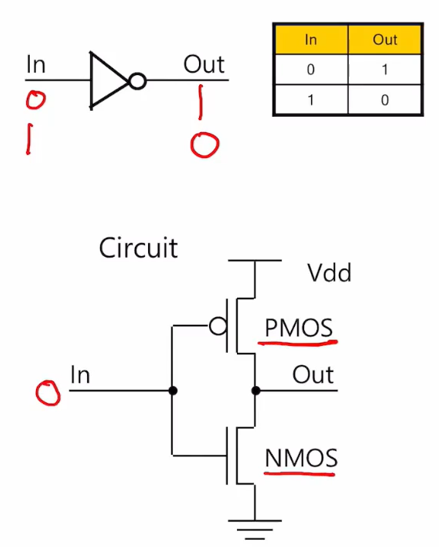

- CMOS 인버터

- CMOS NAND

- CMOS NOR

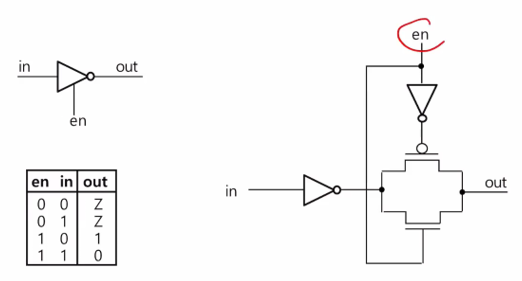

- Tri-State 인버터

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| SRAM 구조 및 동작 원리 (0) | 2024.07.31 |

|---|---|

| 디지털 논리 회로 정리 - 3 (조합, 순차회로) (0) | 2024.07.30 |

| 디지털 논리 회로 정리 - 1 (기본) (0) | 2024.07.22 |

| 통신 프로토콜 UART 동작 원리 (0) | 2024.07.16 |

| FPGA - LUT(Look-Up Table) (0) | 2024.07.12 |