- 조합회로와 순차회로의 구분

1. 조합회로 (Combinational Logic)

값을 저장하지 못한다.

클럭을 사용하지 않는다.

입력의 변화가 출력에 바로 반영된다.

ex) adders, multiplexers, decoders, encoders, gates

2. 순차회로 (Sequential Logic)

값을 저장하는 래치, 플립플롭, 레지스터, 메모리 등의 소자가 있어 상태를 저장

클럭을 사용하여 값을 저장

입력이 변화해도 주로 클럭의 에지에서 값이 반영된다.

- SR(Set Reset) Latch

Set : S 신호가 0일 때 Q값은 1

Reset : R 신호가 0일 때 Q값은 0

S와 R 신호는 0일 때 활성화되는 active-low 신호다.

S=0, R=0은 입력되도록 하지 말아야 한다. S=0, R=0일 때 Q = 1, Q(bar) = 1이지만 S=1, R=1으로 inactive 상태로 돌아왔을 때 딜레이에 의해 Q가 어떤 값인지 불확실해진다.

SR Latch는 기계적 진동에 의한 contact bounce를 제거하기 위하여 사용된다.

- Gated SR Latch

Enalbe(EN) 신호가 있는 SR Latch

EN = 0 : SR Latch의 입력이 1, 1 이므로 값을 유지

EN = 1 : SR Latch의 입력이 S(bar), R(bar)가 되어 출력값이 변할 수 있다.

- D Latch

- Flip Flop

플립플롭(F/F)은 Clock 신호가 변화하는 시점인 edge에 맞추어 동작한다. (Edge-Sensitive) (Latch는 Level-Sensitive)

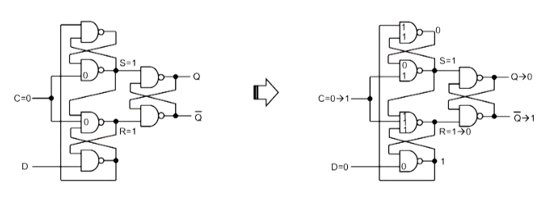

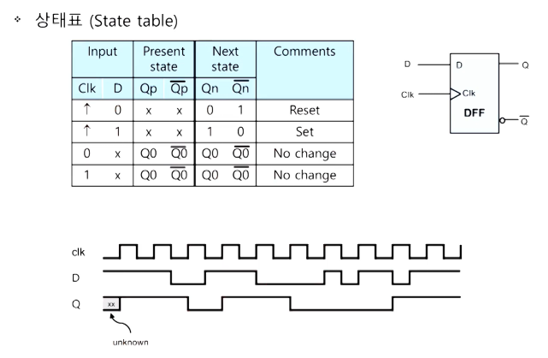

- D F/F

전통적인 구조의 rising edge-triggered이다.

1.

C=0이면 S=1, R=1이므로 Q, Q(bar)는 값을 유지한다.

C=0에서 C=1이 되고 이 때 D=0이라면 오른쪽 SR래치에 S=1, R=0이 입력되어 Q=0이 된다.

따라서 C=0에서 C=1이 되는 순간(rising edge)에 D=0의 값을 받아 Q=0이 된다.

2.

C=0이면 S=1와 R=1이므로 Q, Q(bar)는 값을 유지한다.

C=0에서 C=1이 되고 이 때 D=1이라면 오른쪽 SR래치에 S=0, R=1이 입력되어 Q=1이 된다.

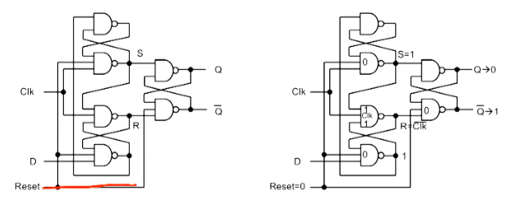

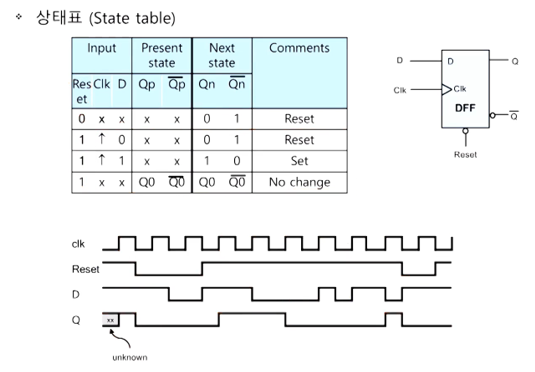

- 비동기 리셋 D F/F

동기 : 클럭 신호에 맞추어 값이 변할 경우

비동기 : 클럭 신호와 상관없이 값이 변할 경우

D F/F의 경우 입력 d의 값이 현재상태 p에 상관없이 다음 상태 n 값으로 된다.

따라서 다음 상태 n을 0으로 만들고 싶다면 d = 0, n을 1로 만들고 싶다면 d = 1을 입력하면 된다.

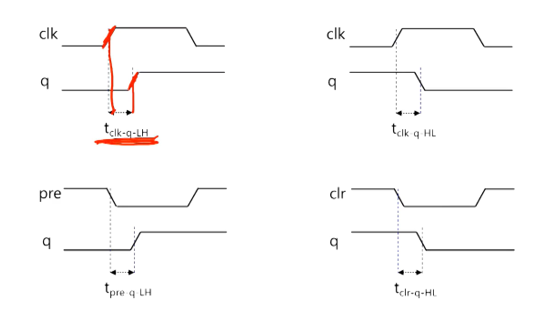

- Propagation Delay

Propagation delay time : 전달(전파) 지연 시간

- 셋업(Setup) & 홀드(Hold) 시간

Setup Time : Clock의 edge 전 미리 입력 데이터가 안정되어야 하는 최소 시간

Hold Time : Clock의 edge 후 입력 데이터가 유지되고 있어야 하는 최소 시간

출처 : http://www.kocw.net/home/cview.do?cid=8af71bd432c850ff 금오공대 강의

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| Cache 구조 및 동작 원리 (0) | 2024.08.01 |

|---|---|

| SRAM 구조 및 동작 원리 (0) | 2024.07.31 |

| 디지털 논리 회로 정리 - 2 (논리 회로) (0) | 2024.07.23 |

| 디지털 논리 회로 정리 - 1 (기본) (0) | 2024.07.22 |

| 통신 프로토콜 UART 동작 원리 (0) | 2024.07.16 |