Cache

Cache는 컴퓨터 시스템에서 데이터 접근 속도를 향상시키기 위해 사용하는 고속 메모리다. CPU와 메인 메모리(DRAM) 간의 데이터 전송 속도 차이를 줄여서 전체 시스템의 성능을 개선하는 역할을 한다.

Cache는 일반적으로 SRAM으로 구성되어 있으며, DRAM보다 속보가 빠르며 비휘발성의 성질을 가지고 있다.

- cache 계층

1. L1 캐시 : 가장 빠르고 작은 캐시로, CPU 코어에 직접 내장되어 있다. 데이터 접근 속도가 매우 빠르지만 용량은 작다.

2. L2 캐시 : L1 캐시보다 느리지만 더 큰 용량을 가지며, CPU 코어에 통합되거나 별도의 캐시 모듈로 존재할 수 있다.

3. L3 캐시 : 여러 CPU 코어 간에 공유되는 캐시로, L2보다 더 느리지만 훨씬 더 큰 용량을 가지고 있다.

- cache Hit

CPU가 원하는 데이터가 이미 cache에 적재되어 있는 상태

- cache miss

CPU가 원하는 데이터가 캐시에 없는 상태

- latency

데이터 요청부터 처리 시작하기까지의 걸리는 시간

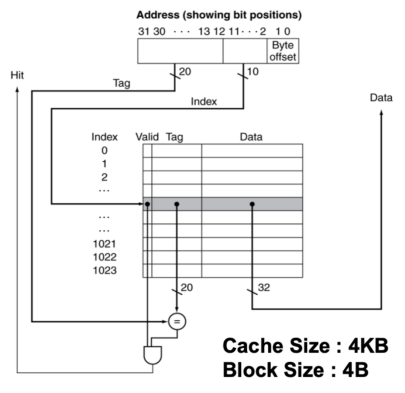

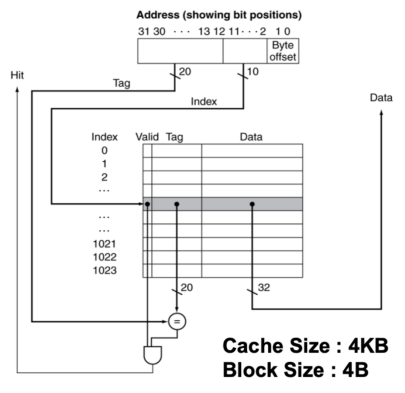

위 그림에서 제일 위 Address는 CPU가 Cache Controller에게 보내는 메모리 주소에 해당한다.

위 그림에서의 Address는 총 32비트 Tag, Index, Offset으로 이루어져 있다.

- Tag

1. 실제 메모리의 어느 부분과 대응되는지 식별하는데 사용된다.

- Index

1. 캐시 내의 특정 세트를 지정하는 데 사용된다. 인덱스 값은 캐시의 크기와 연관이 있다. (10비트의 Index를 가지게 되면 인덱스 값은 1024개가 된다.)

- Byte Offset

1. 캐시 라인 내에서 특정 바이트를 지정하는 데 사용된다. 위 예에서는 4비트 Offset을 사용하고 있으므로 캐시 라인당 16바이트를 지정할 수 있다.

Cache 동작 과정

1. CPU가 메모리 주소를 요청할 때, 캐시 Controller는 Address의 Index 부분을 사용하여 특정 캐시 라인을 선택한다.

(Index 부분이 0000000010이면 캐시 라인의 Index 2를 확인한다.)

2. Index 필드를 사용하여 Cache의 특정 라인으로 접근한다.

3. 해당 라인의 유효 비트를 확인한다.

4. 유효 비트가 설정되어 있으면, Tag 필드를 비교하여 Cache에 데이터가 있는지 확인한다.

4.1. Index의 Tag가 일치하면 Cache Hit에 해당되어 Offset을 사용하여 필요한 데이터를 추출하여 CPU로 전달한다.

4.2. Tag가 일치하지 않거나 유효 비트가 설정되지 않은 경우, Cache Miss에 해당되어 Data를 메인 메모리에서 읽어온다.

읽어온 데이터는 Cache에 저장되며, 기존 데이터를 교체하거나 새로운 위치에 저장된다. 그 후 CPU로 데이터가 전달된다.

캐시의 종류

1. 직접 매핑 (Direct Mapped Cache)

- 각 메모리 블록이 하나의 고정된 캐시 라인에 매핑된다.

- 구현이 간단하지만, 하나의 Index에 대해 다른 Tag 요청이 들어오게 되면 Cache Miss를 계속해서 발생 시킨다.

2. 완전 연관 매핑 (Fully Associative Cache)

- 모든 메모리 블록이 Cache의 모든 라인에 매핑될 수 있다.

- 구현이 복잡하고, 모든 Cache Line을 확인해야 하기 때문에 검색 시간이 오래 걸린다.

3. 집합 연관 매핑 (Set Associative Cache)

- Cache를 여러 집합으로 나누고, 각 집합 내에서 완전 연관 매핑을 사용한다.

- 성능과 구현의 균형을 맞추는 방식이다.

- 일반적으로 4, 16 way를 많이 사용한다.

캐시 갱신 정책

캐시 미스가 발생할 때, 새로운 데이터를 캐시에 저장하는 방법에는 여러 가지가 있다.

1. Write-through : 데이터를 캐시에 저장하면서 동시에 메인 메모리에도 저장한다.

2. Write-back : 데이터를 캐시에만 저장하고, 캐리 라인이 교체될 때만 메인 메모리에 저장한다.

캐시 교체 알고리즘

캐시가 가득 찼을 때, 새로운 데이터를 저장하기 위해 기존 데이터를 교체해야 한다. 이를 위한 알고리즘으로는 다음과 같은 것들이 있다.

1. LRU (Least Recently Used) : 가장 오랫동안 사용되지 않은 데이터를 교체한다.

2. FIFO (First In, First Out) : 가장 먼저 들어온 데이터를 교체한다.

그 외 Random, LFU 등 여러 알고리즘이 사용된다.

■ 추가 학습 내용

위와 같이 CPU에서 00001의 메모리 주소의 값을 찾기 위해 데이터를 전달하면 우선 Cache 메모리에 인덱스와 태그를 비교한다.

cache memory의 001 인덱스를 확인하여 태그를 비교했을 때 1. 비어있거나 2. 태그가 일치하지 않은 경우 cache Miss이기 때문에 00001 주소의 메모리에서 데이터를 가저옴과 동시에 태그 값을 변경한다.

Memory가 총 4096 블록이 있고, 캐시 사이즈가 256bytes 캐시 Block 사이즈가 4bytes이기 떄문에 캐시 라인은 64라인이 존재하게 된다.

Tag는 캐시 라인이 64라인이고, Memory Block이 4096이기 때문에 Tag는 6bit가 되는 것이다.

만약 Memory Block이 8192가 되면 캐시 라인이 64 그대로 유지된다면 Tag는 7bit가 될 것이다.

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| DRAM 구조 및 동작 원리 (2) (0) | 2024.08.09 |

|---|---|

| DRAM 구조 및 동작 원리 (1) (0) | 2024.08.02 |

| SRAM 구조 및 동작 원리 (0) | 2024.07.31 |

| 디지털 논리 회로 정리 - 3 (조합, 순차회로) (0) | 2024.07.30 |

| 디지털 논리 회로 정리 - 2 (논리 회로) (0) | 2024.07.23 |