Synopsys를 통해 Synthesis 합성을 하기 위해서는

1. verilog-HDL .v 파일

2. 게이트 정보가 담긴 .db 파일

3. .sdc 파일 혹은 제약 정보가 필요하다.

remove_design -all //초기화

set FILE "counter" //모듈명 선언

set synthetic_library "../LIB/DBH_1225RS13SD_GEMV1P8V_FF_1P32V_M40C.db"

//라이브러리 위치 지정 및 파일 지정

//db 파일을 넣어줘야 한다.

set search_path "../LIB/"

set target_library "../LIB/DBH_1225RS13SD_GEMV1P8V_FF_1P32V_M40C.db"

//타겟 라이브러리 지정 및 파일 지정

//db 파일을 넣어줘야 한다.

analyze -library WORK -format verilog {./rtl/counter.v}

//rtl 파일 경로 및 파일 지정

elaborate $FILE -architecture verilog -library WORK -update

//문법 에러 등 체크

current_design $FILE

link

uniquify

set clk [get_ports clk]

//sdc 파일 경로를 직접 입력하거나 clk 조건을 직접 입력해주면 된다.

create_clock -period 12.5 [get_port clk]

check_design

compile_ultra

//ultra를 통해 compile 작업 실행

report_reference > ./report/reference.rpt

report_timing -delay min > ./report/min_timing.rpt

report_hierarchy > ./report/constraint.rpt

report_cell > ./report/cell.rpt

report_area > ./report/area.rpt

report_power > ./report/power.rpt

//report 파일 생성

write -format verilog -hier -out ./mapped/$FILE.v

write_sdf ./mapped/$FILE.sdf

write_sdc ./mapped/$FILE.sdc

// .v .sdf .sdc 파일 생성

합성을 위한 스크립트 파일을 위와 같이 작성해준다.

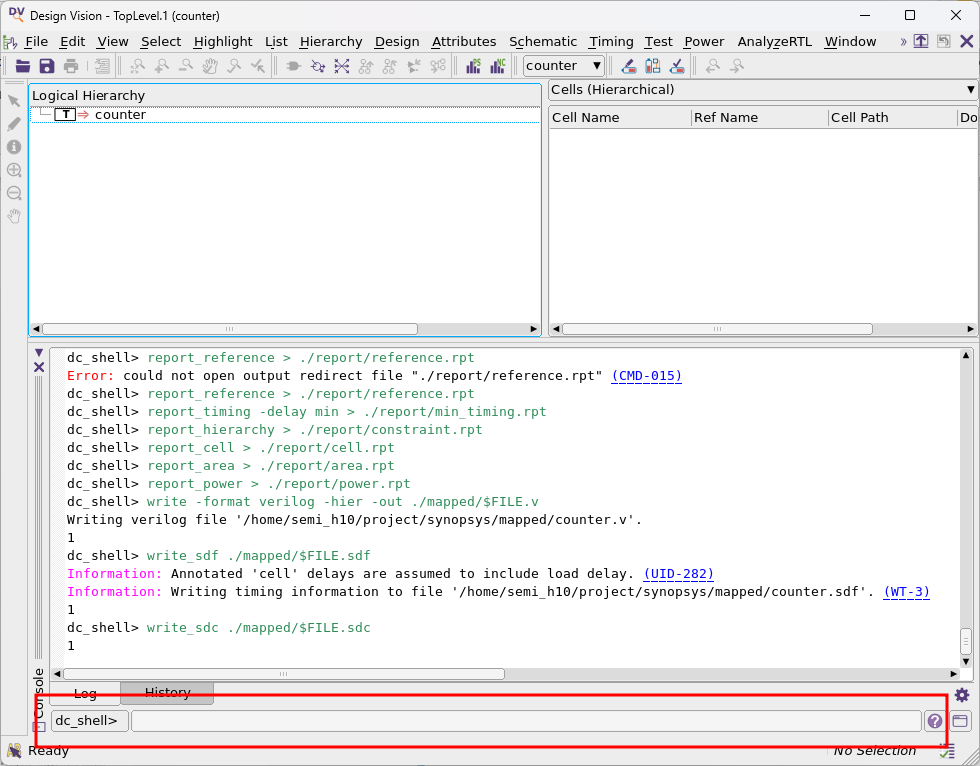

명령어를 이용한 방법

dc_shell -f [스크립트 파일명]

GUI를 이용한 방법

dc_shell -gui

위 명령어를 통해 Design Vision 프로그램을 실행 시킬 수 있다.

GUI를 통해 파일을 불러오거나 shell을 이용하여 스크립트 파일을 실행할 수 있다.

스크립트 파일이 실행중에 Error가 발생할 경우 Error 위치를 발견하기 쉽진 않다.

GUI의 shell을 이용하게 되면 한 줄 한 줄 코드의 Error 발생 여부를 확인하여 보다 확실하게 코드 이상 유무를 파악할 수 있다.

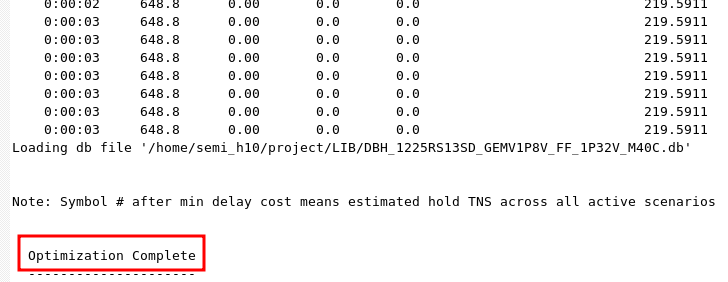

스크립트 코드에 이상이 없는경우 Compile이 정상적으로 완료되면 Complete를 통해 확인할 수 있다.

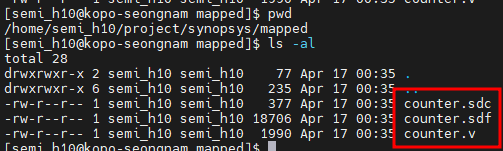

write -format verilog -hier -out ./mapped/$FILE.v

write_sdf ./mapped/$FILE.sdf

write_sdc ./mapped/$FILE.sdc스크립트 파일을 보게되면 .v .sdf .sdc 파일 생성 경로를 위와 같이 지정해주었다.

전체 스크립트 파일이 정상적으로 동작하게 될 경우 write 명령어를 통해 .v .sdf .sdc 파일이 정상적으로 생성된 것을 확인 할 수 있다.

728x90

'Semiconductor > Synthesis, PnR' 카테고리의 다른 글

| Synthesis - Clock Gating (이론 및 Syn 후 Simulation 확인) (0) | 2024.09.25 |

|---|---|

| Innovus - P&R (SETUP ~ GDSII) (0) | 2024.06.05 |

| Cadence - Synthesis / Pre_layout Simulation (0) | 2024.04.09 |