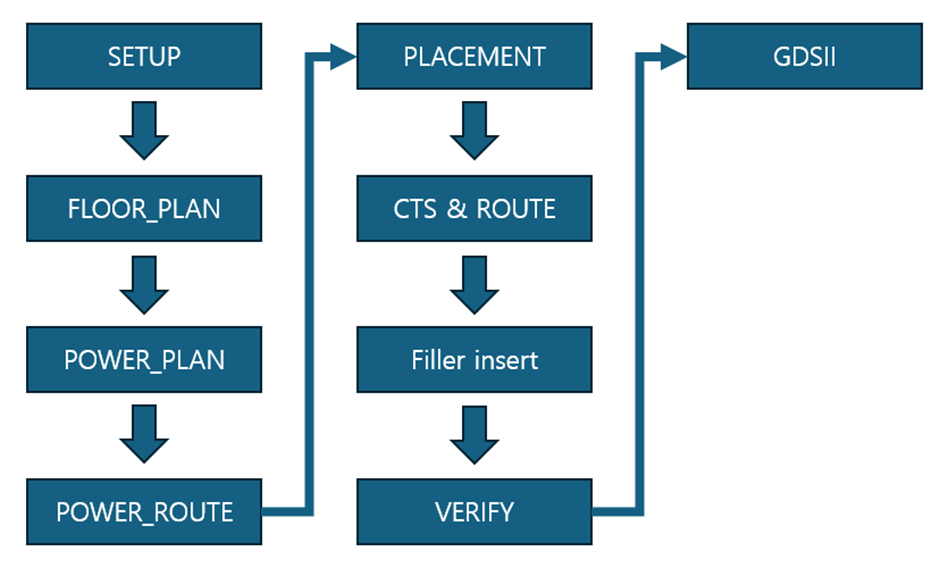

P&R의 SETUP ~ GDSII 파일 생성

P&R은 위 Layout 절차를 따른다.

Netlist : Design Netlist - Verilog file

SDC : Constraint file

LEF : Physical Libraries

LIB : Timing Libraries

- P&R 이후

GDS : Physical Layout

Netlist : P&R 후 Netlist

SDF : Standart Delay Format

P&R을 위한 파일 설계자, 공정사

1. 설계자 제공 파일

- Netlist 파일 : 합성 결과물

- sdc 파일 : 디자인 제약 조건

2. 공정사 제공 파일

- 디지털 라이브러리, lef 파일

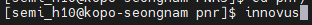

Innovus를 실행하게 되면 기본적으로 2개의 파일이 생성된다.

1. 로그 파일

- innovus.log : 기본 로그 파일

- innovus.logv : 기본 로그 파일의 상세 정보

2. 명령 파일

- innovus에서 수행할 작업을 지정하고 자동화하는데 사용된다.

- innovus.cmd : 명령어를 실행하거나 스크립트를 실행 뒤 실행된 명령어가 저장된다.

lib, netlist 파일 등 상대 경로를 잘파악하여 innovus를 실행 시킬 위치를 고려하여 실행 시킨다.

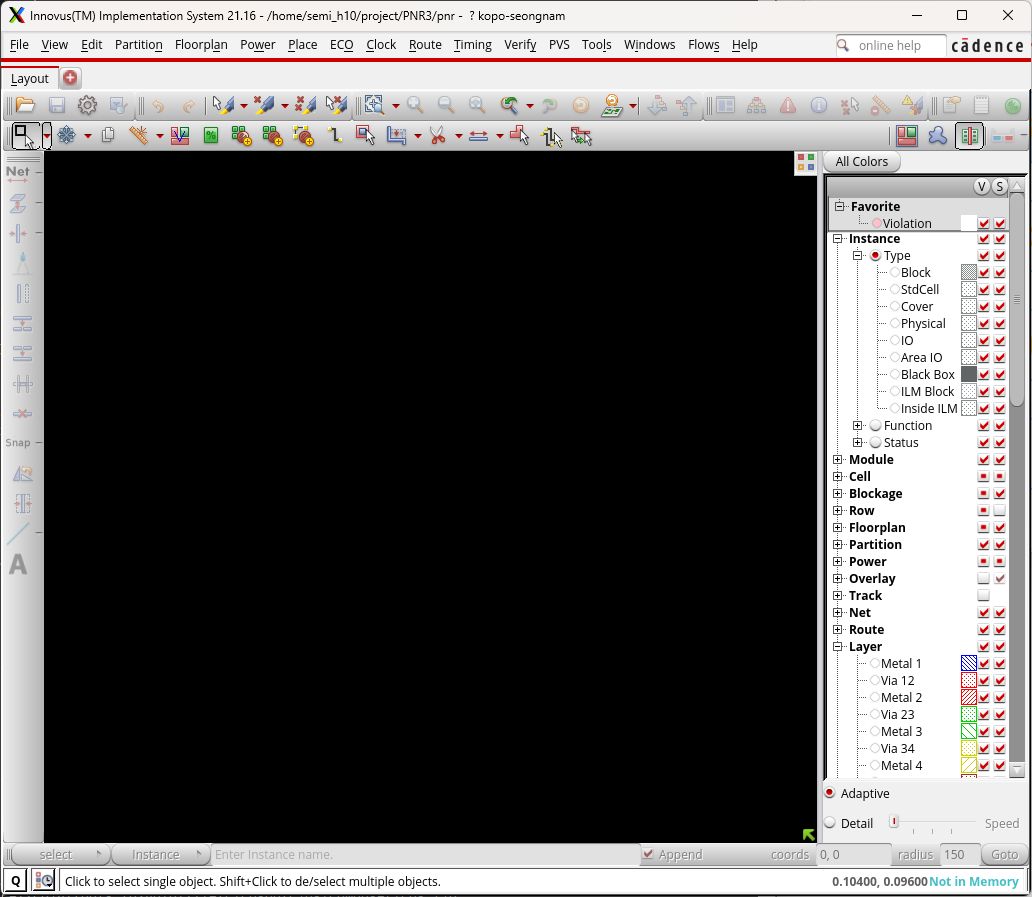

SETUP

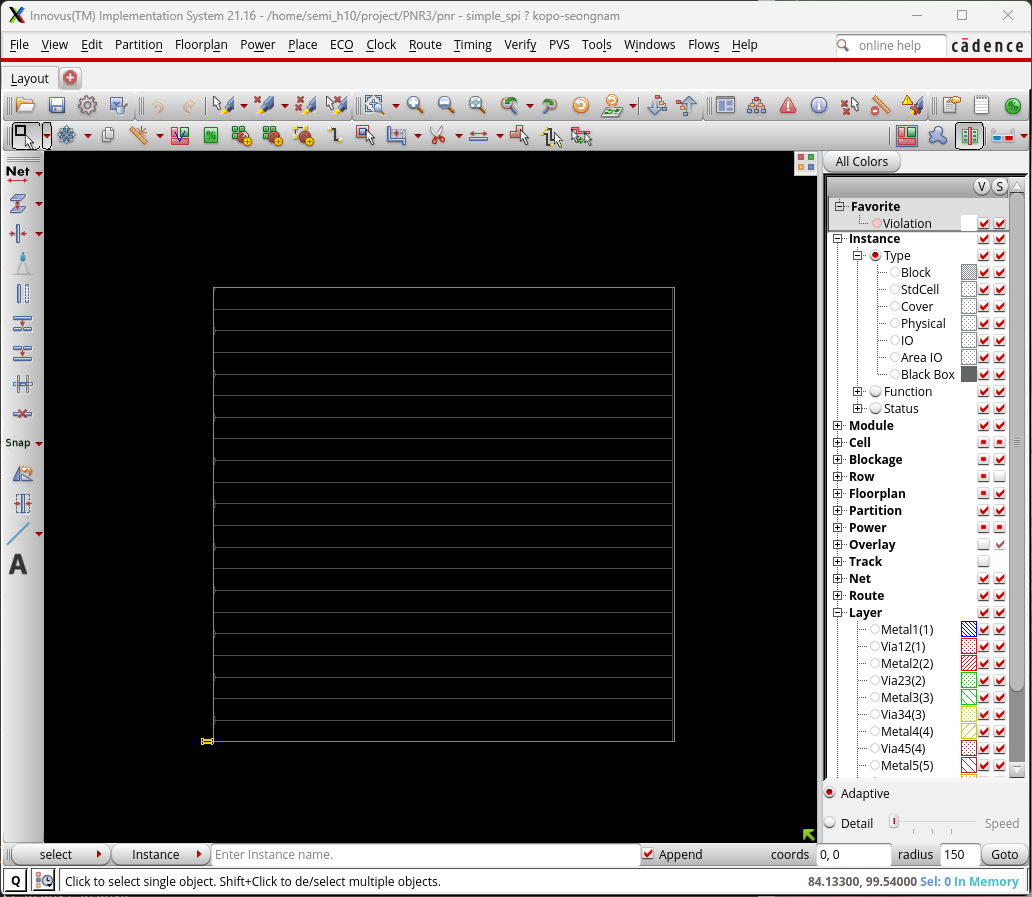

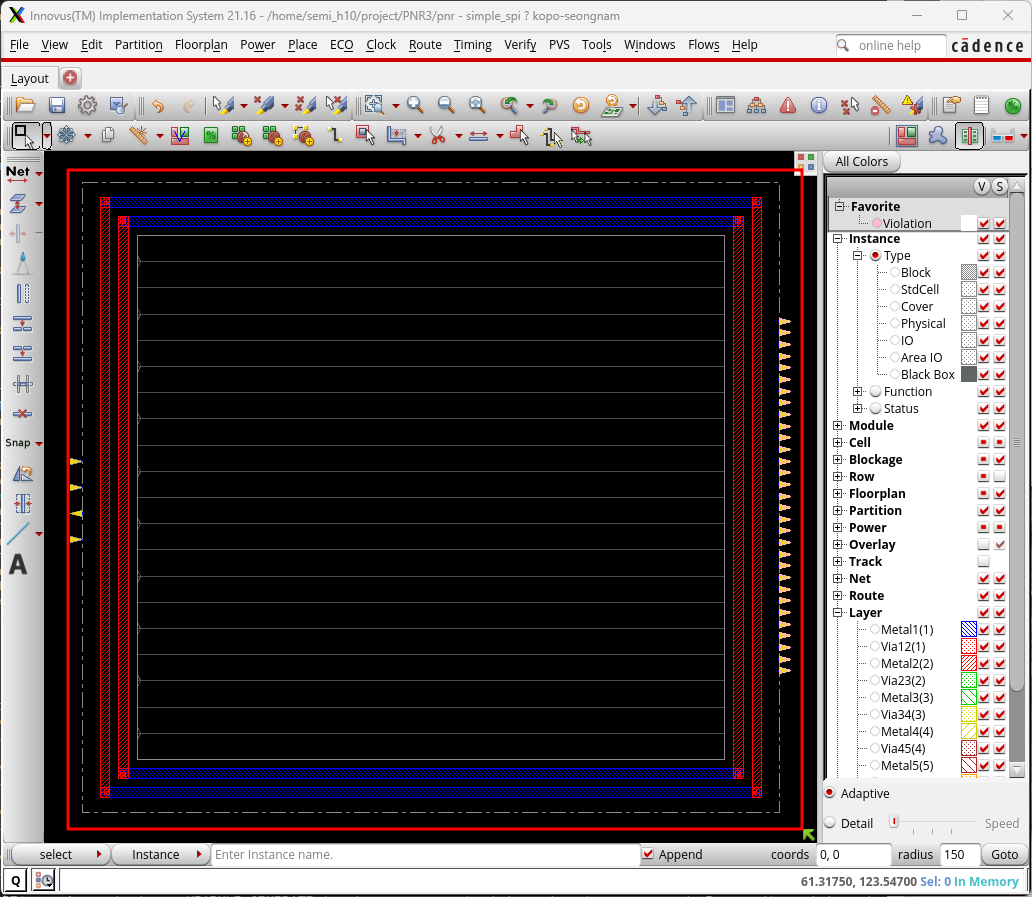

innovus가 실행된 화면이다.

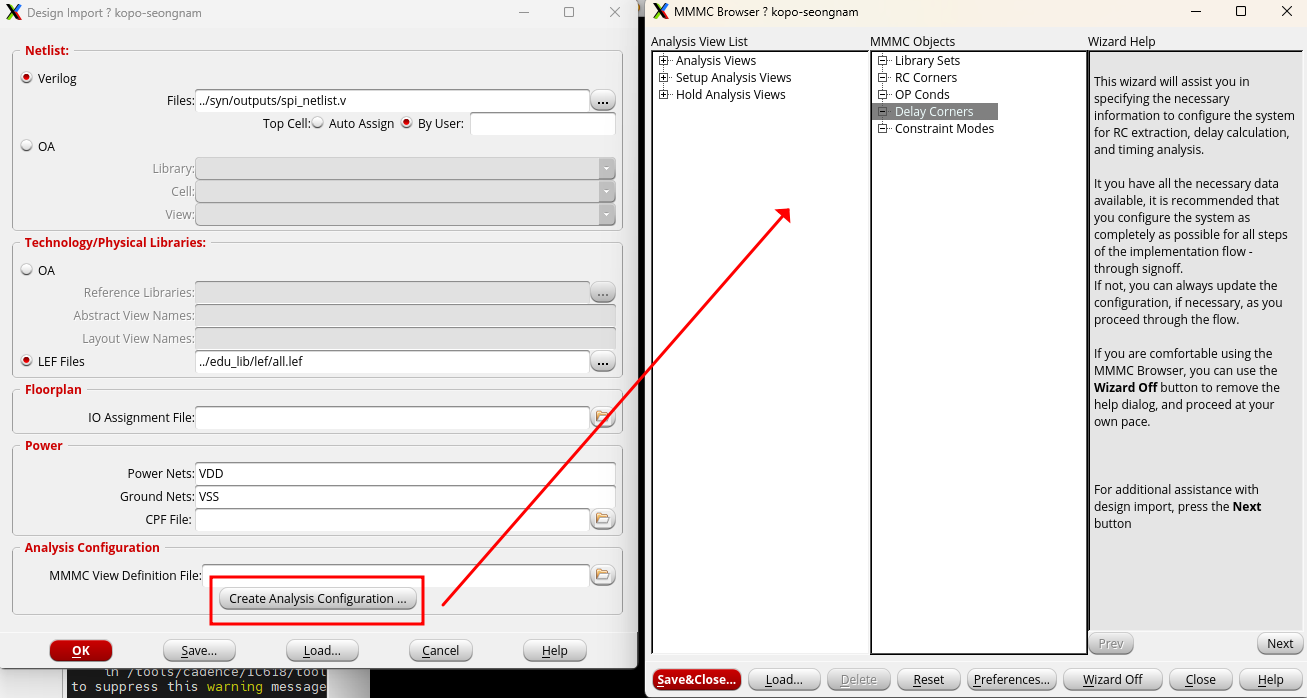

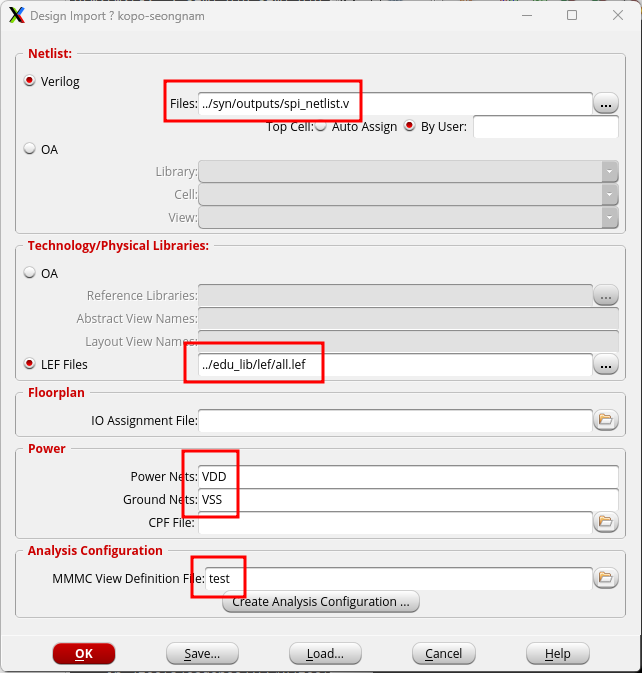

P&R을 하기 위한 합성을 통해 생성된 netlist 파일을 추가한다.

lef 파일은 라이브러리의 셀(cell)에 대한 구성 정보를 담고 있다.

Power 항목을 통해 Power와 Ground Nets에 대한 이름을 지정한다.

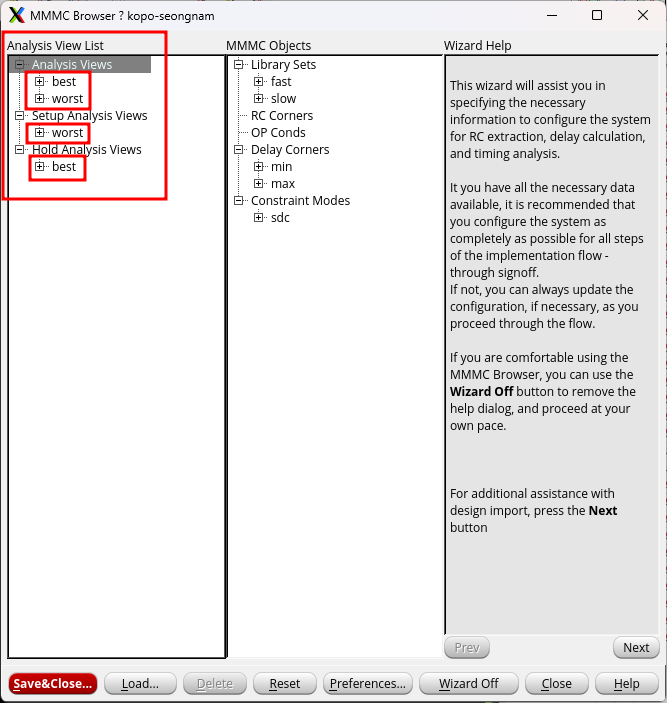

MMMC(Multi Mode Multi Corner)

1. MMMC(Multi Mode Multi Corner) 조건을 설정하는 우측 부분이 LIB 파일들을 추가하고

2. 좌측의 설정에 따른 분석뷰를 세팅한다.

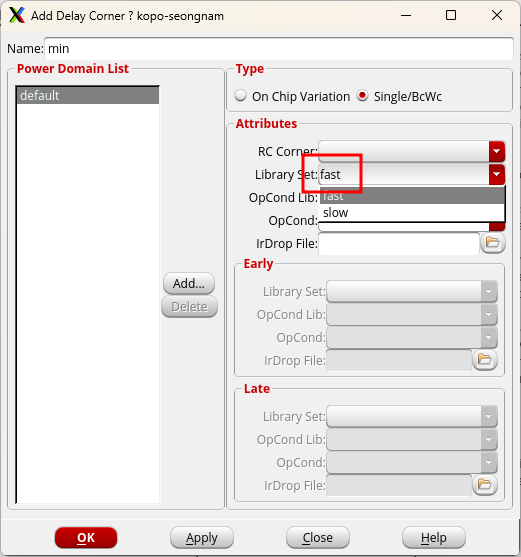

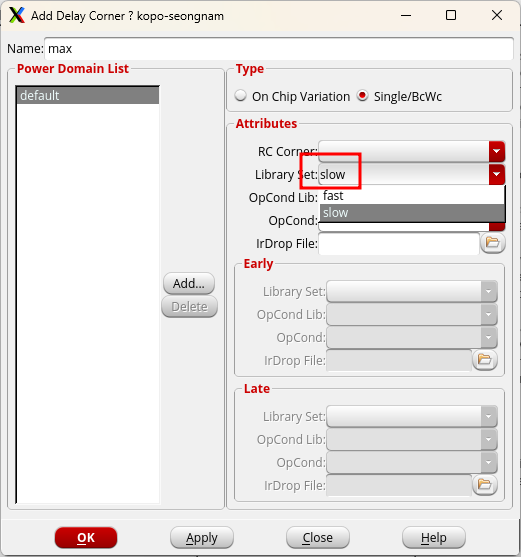

Delay corner를 설정할 때 min -> fast / max -> slow로 설정한다.

fast, slow는 딜레이가 가장 빠를 때 가장 느릴 때 LIB에 해당한다.

fast는 딜레이가 가장 빠르기 때문에 Delay corner가 min에 해당하고, slow는 딜레이가 가장 느리기 때문에 Delay corner가 max에 해당한다.

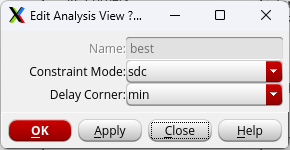

좌측의 분석뷰를 위한 Delay Corner에 min max를 넣는 기준도 best case(딜레이가 가장 빠를 때)와 worst case(딜레이가 가장 느릴 때)를 구분하여 생성한다.

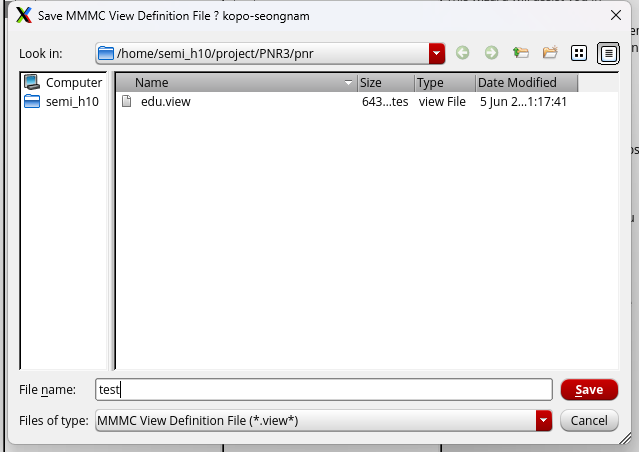

MMMC View Definition File을 저장하고 불러오는 것이 가능하다.

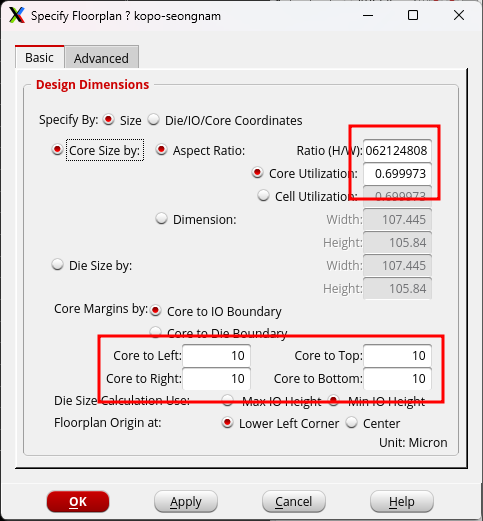

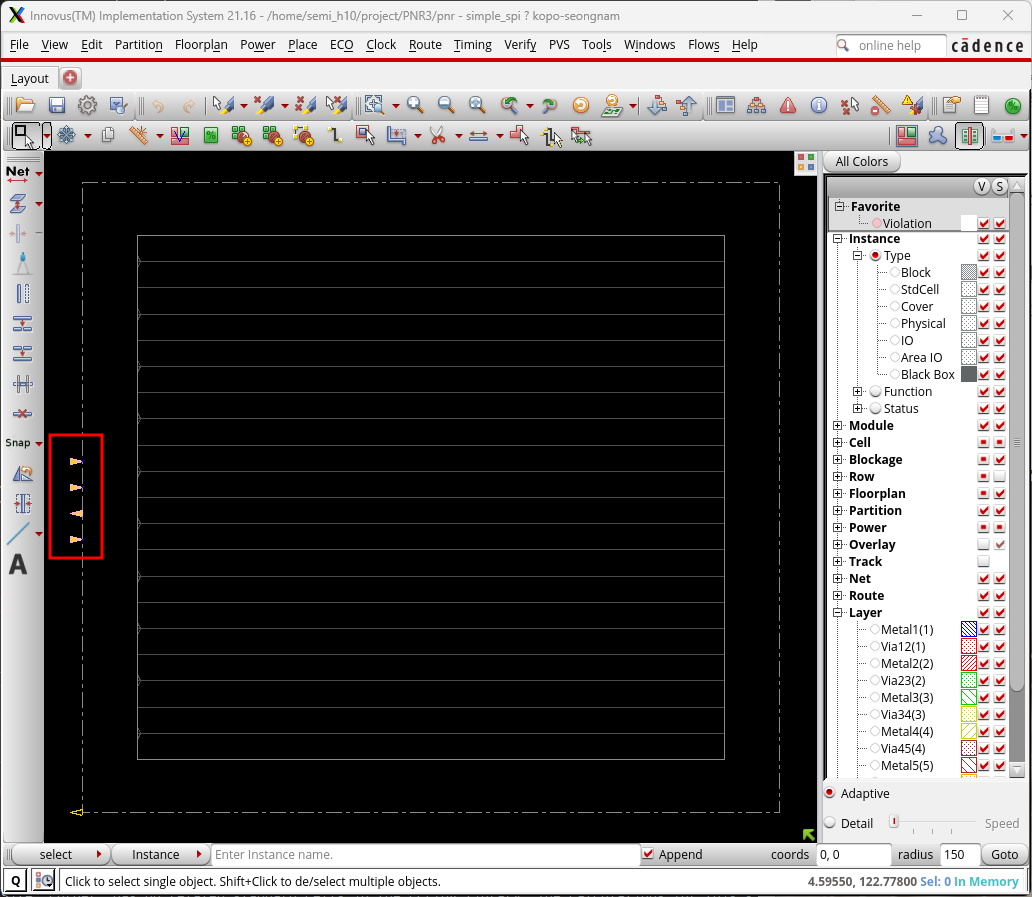

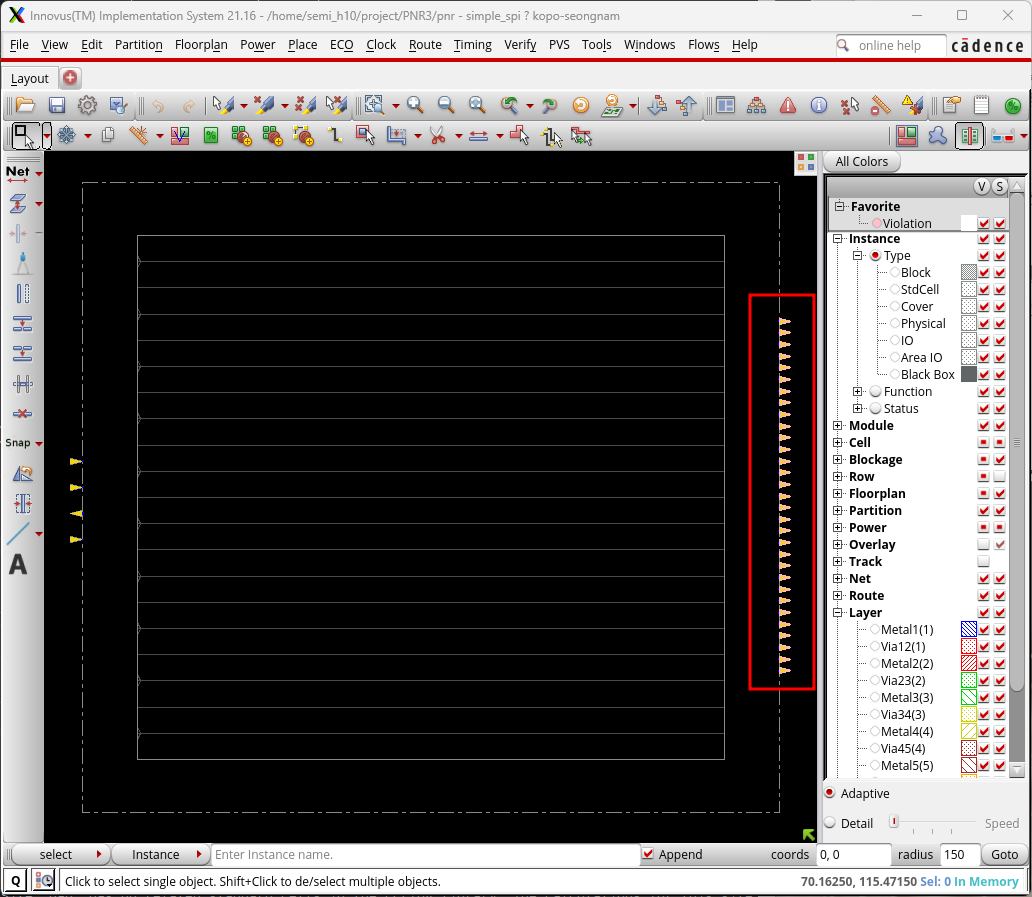

Import Design을 마치게 되면 위와 같이 Cell과 VDD, VSS를 배치하기 위한 모형이 생성된다.

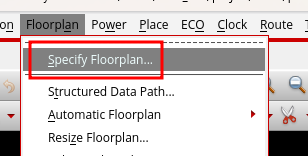

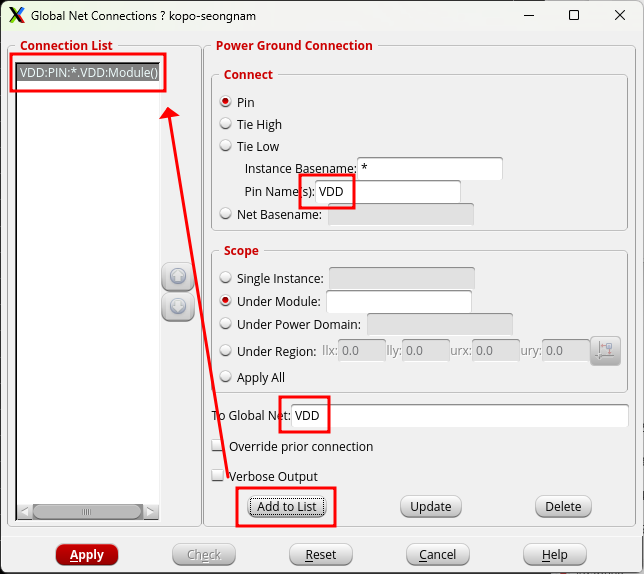

FLOOR_PLAN

Floor_Plan은 설계가 배치될 전체 칩 여역을 설정하기 위함이다.

Core Size by를 통해 칩 영역의 크기를 설정하고, Core Margins를 통해 Core로부터 일정 거리 떨어진 영역을 생성한다.

이렇게 Core Margins를 통해 생성된 영역에는 주로 VDD와 VSS가 들어가게 된다.

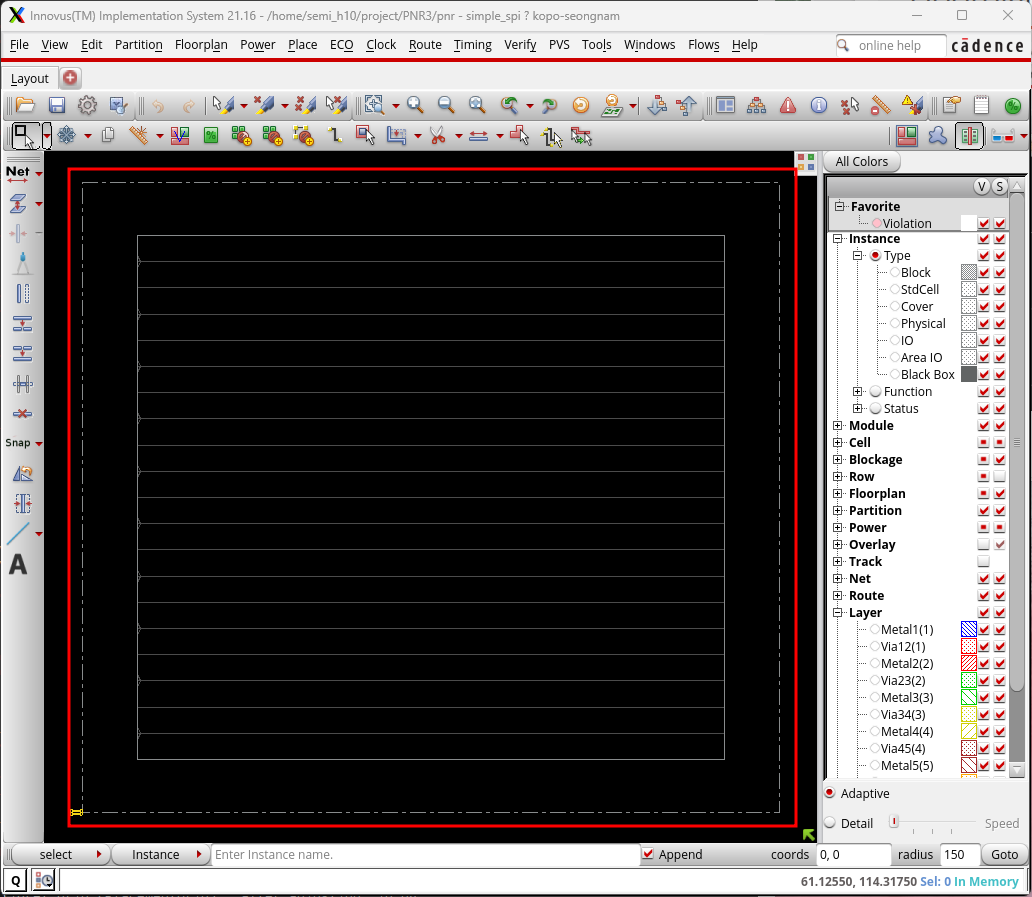

POWER PLAN

Power Plan은 칩 내부의 모든 회로에 안정적이고 균일한 전력을 공급하는 것을 보장한다.

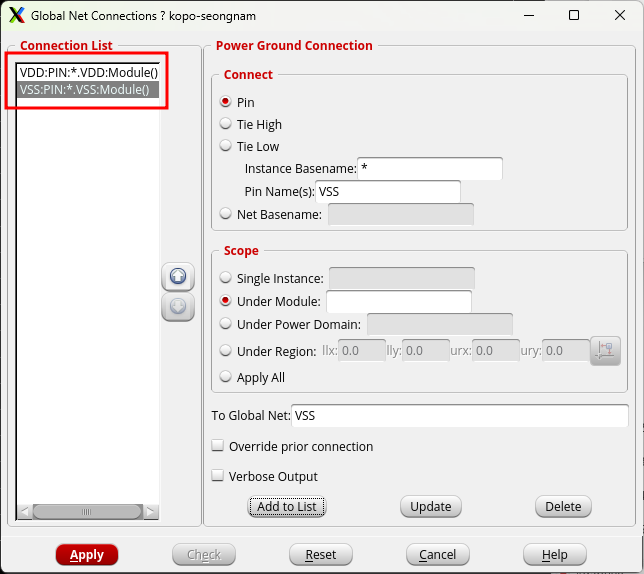

칩 내의 모든 셀, 매크로, IP 블록 등에게 전력(VDD)과 그라운드(VSS) 신호를 연결하기 위한 설정이다.

netlist에서 작성한 VDD, VSS를 Pin Name(VDD, VSS)에 넣고,To Global Net에는 Import Design에서 Power / Ground nets(VDD, VSS)를 넣어준다.

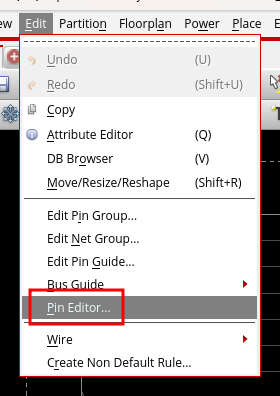

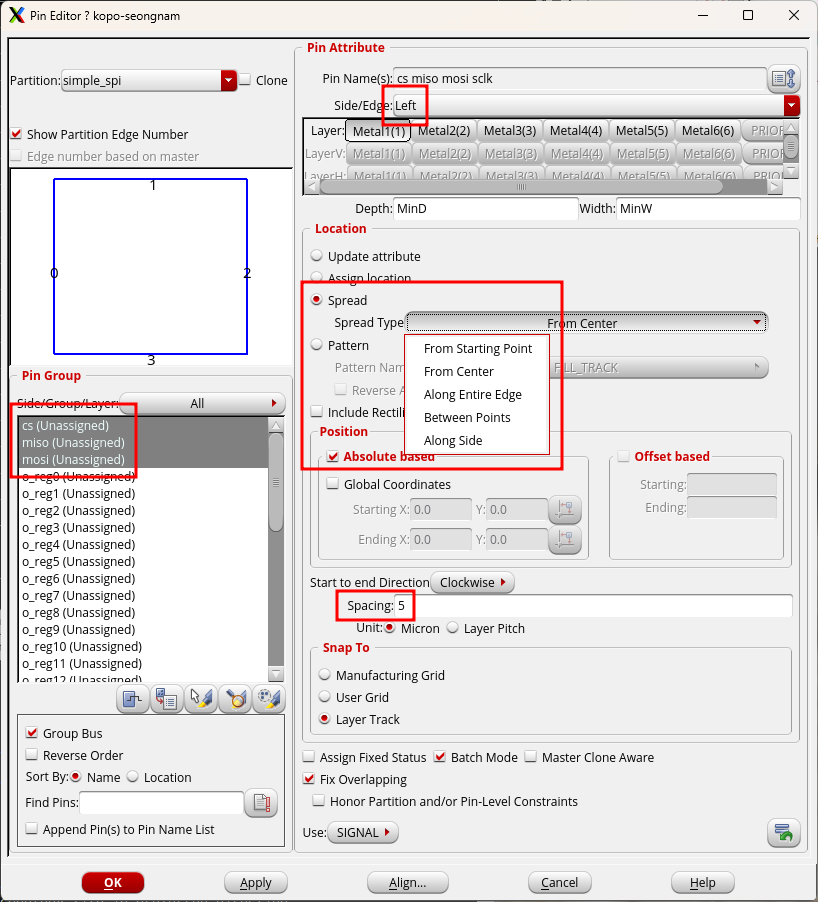

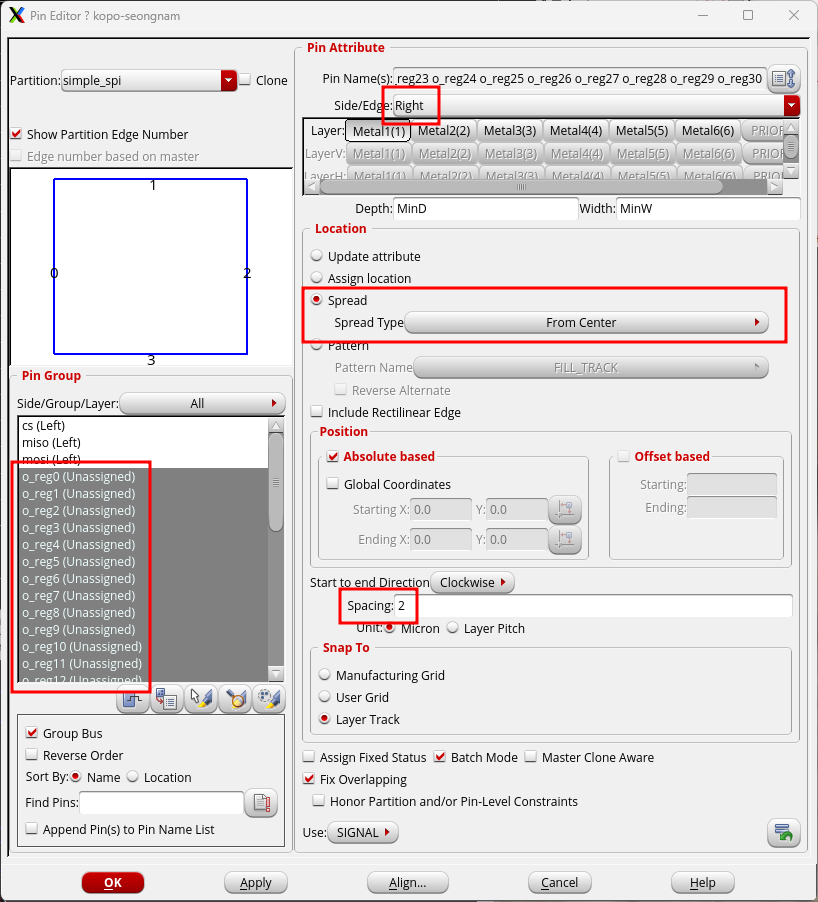

Pin Editor

netlist를 정의된 Pin들을 배치하기 위한 설정이다.

좌측의 배치할 핀들을 선택하고, Location 항목을 통해 Pin들을 위치할 설정을 해준다.

일반적으로 Spread를 설정하여 상단의 Side/Edge를 통해 방향을 선택하고 Spread Type을 통해 어떤 기준으로 퍼트릴 것인지 결정한다.

그 아래 Spacing을 통해 각 핀들이 얼만큼 간격을 가질지 설정할 수 있다.

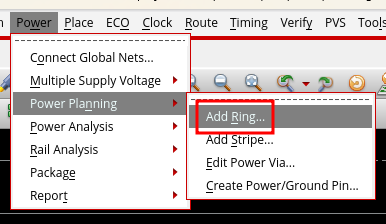

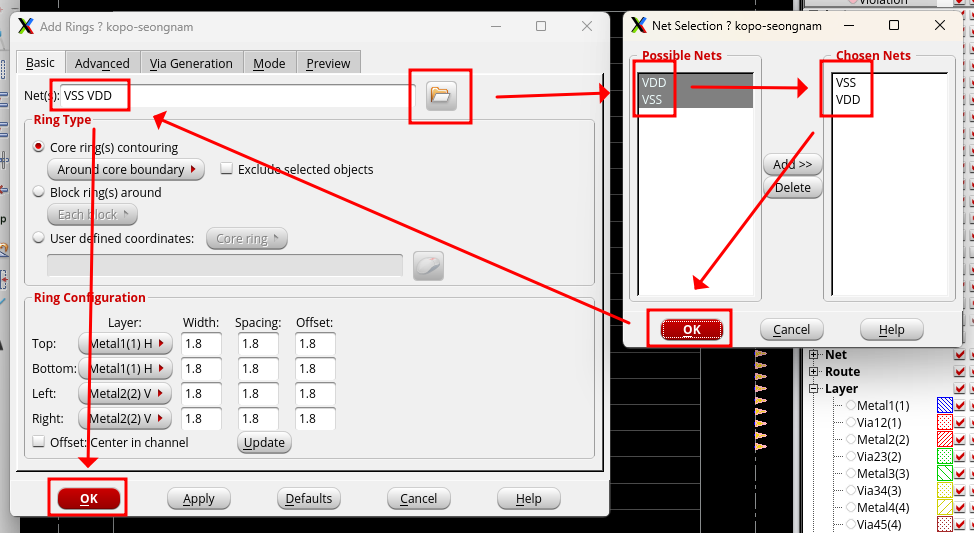

Power Plan (이어서)

Power Plannig에서 Add Ring은 코어를 중심으로 VDD / VSS를 삽입하는 단계에 해당한다.

VDD / VSS 삽입할 Layer 선택 및 width, spacing, offset을 설정한다.

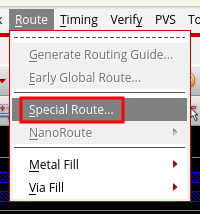

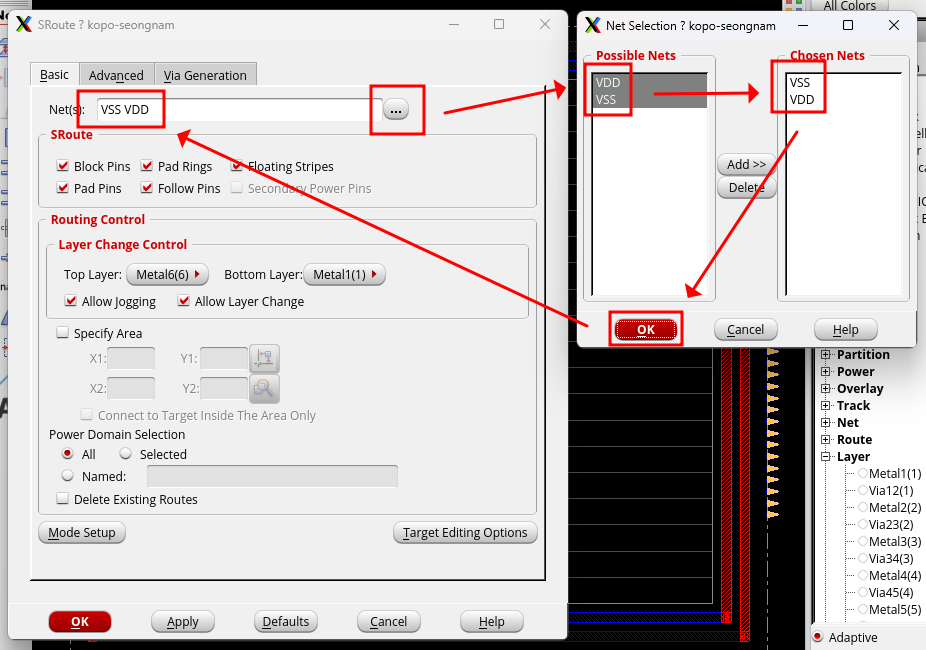

Power Routing

Power Routing은 안정적인 전력 공급을 보장하기 위한 설정이다.

전력과 그라운드 신호를 모든 회로 요소에 안정적으로 전달하여, 회로가 예상대로 동작할 수 있도록 한다.

Special Route는 칩 설계에서 특정한 신호, 특히 전력(VDD)와 그라운드(VSS), 클럭, 리셋 신호 등을 처리하기 위해 수행되는 배선 작업이다.

즉, 전력과 그라운드 신호가 칩 내 모든 셀과 블록에 안정적으로 전달되로고 보장하는 전력 무결성을 유지한다.

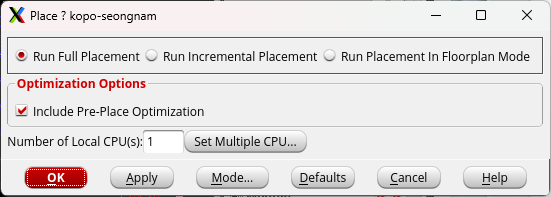

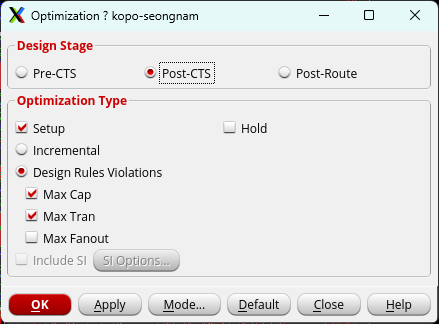

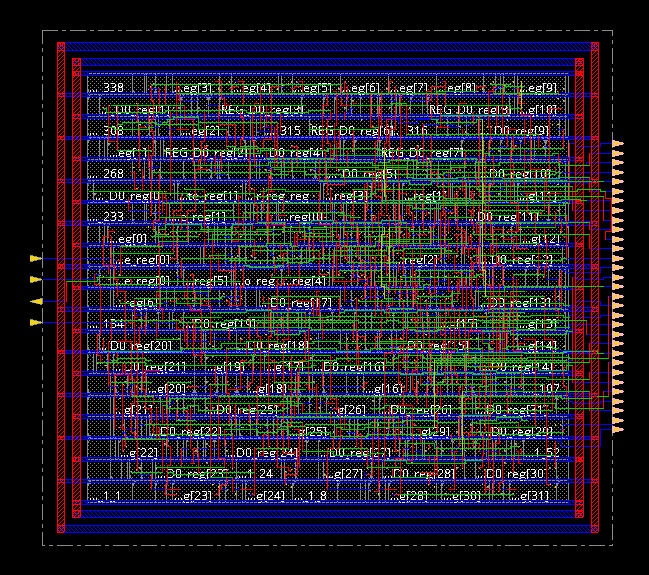

Placement

Placement는 칩 설계 과정에서 각 셀과 매크로 블록을 물리적 위치에 배치하는 단계로, 설계의 성능, 전력 소비, 제조 가능성에 큰 영향을 미친다.

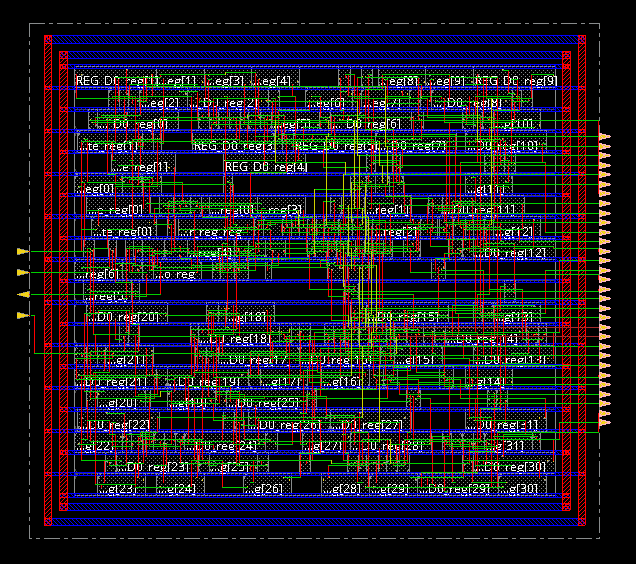

위와 같이 칩에 Cell들이 배치된다.

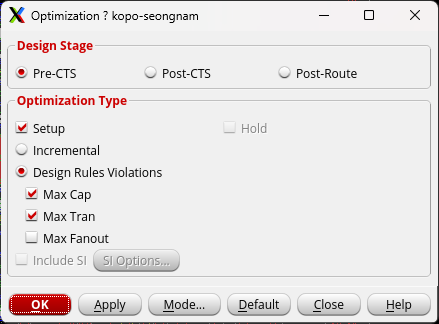

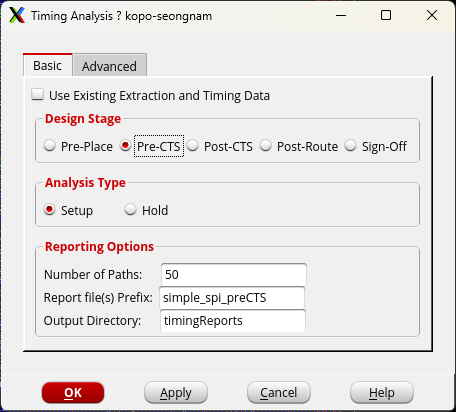

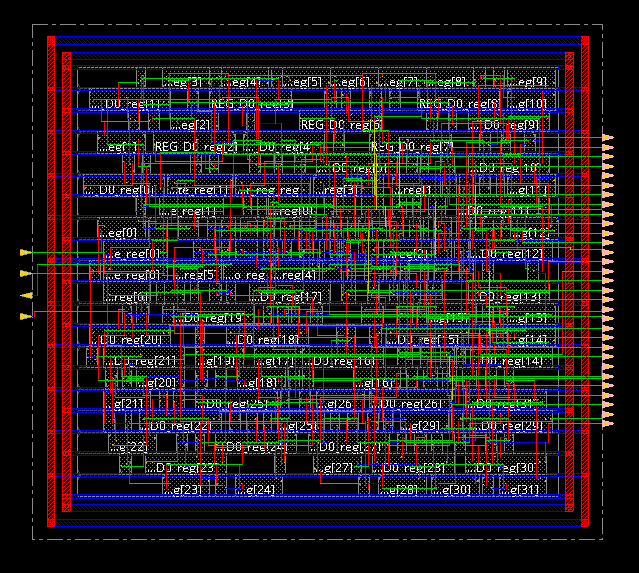

Pre-CTS

CTS(Clock Tree Synthesis) : 회로에서 클럭이 가까우면 클럭 신호가 빠르게 들어가고 멀면 클럭 신호가 느리게 들어간다. 거리에 따라 클럭 신호가 다르게 들어가면 클럭 기준이 서로 달라질 수 있기 때문에 동일한 클럭이 전달될 수 있도록 맞춰주는 것이 CTS를 의미한다.

P&R에서는 CTS가 매우 중요한 작업 중 하나다.

Pre-CTS는 현재 배친된 Cell 상태만을 가지고 Routing되기 전에 먼저 CTS를 수행하는 것이다.

Pre-CTS 이후 Cell 배치가 변경된 것을 확인할 수 있다.

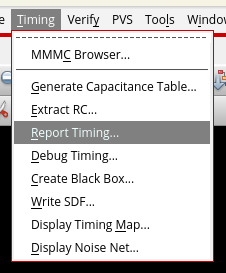

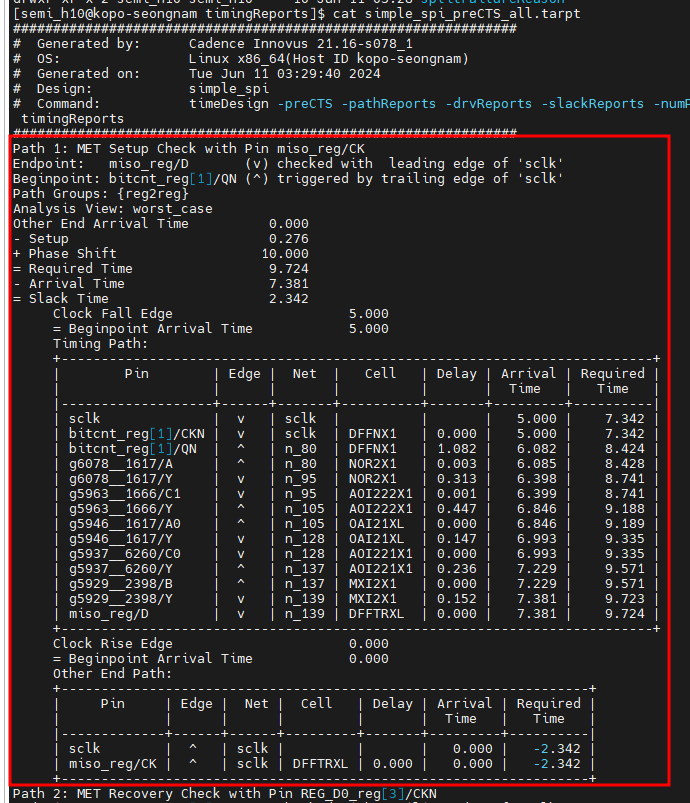

Report Timing을 통해 Pre-CTS에 대한 결과물을 확인할 수 있다.

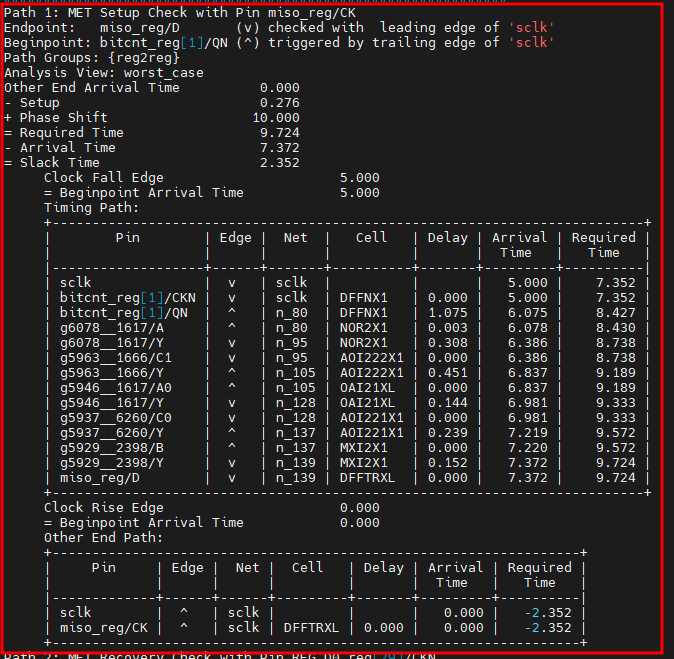

Timing Report를 통해 특정 패스를 확인할 수 있다.

Path : 타이밍 분석에서 사용되는 특정 패스의 이름 또는 식별자다.

Endpoint : 데이터가 도착하는 지점을 나타낸다.

Beginpoint : 데이터가 출발하는 지점을 나타낸다.

Path Groups : 패스가 속하는 그룹을 나타낸다.

Required Time : 데이터가 도착해야 하는 시간을 나타낸다. 이 시간 내에 데이터가 도착하지 않으면 회로가 오작동할 수 있다.

Arrival Time : 데이터가 실제로 도착한 시간을 나타낸다.

Slack Time : 실제 도착한 시간과 필요한 도착 시간 사이의 여유 시간을 나타낸다. 이 값이 양수인 경우, 타이밍 요건을 충족한다는 것을 알 수 있다.

Timing Path : 데이터가 흐르는 각 구성 요소에 대한 정보를 제공한다. Delay, Arrival Time, Required Time 등이 나열된다.

Other End Arrival Time : 다른 끝점에서 데이터가 도착한 시간을 나타낸다.

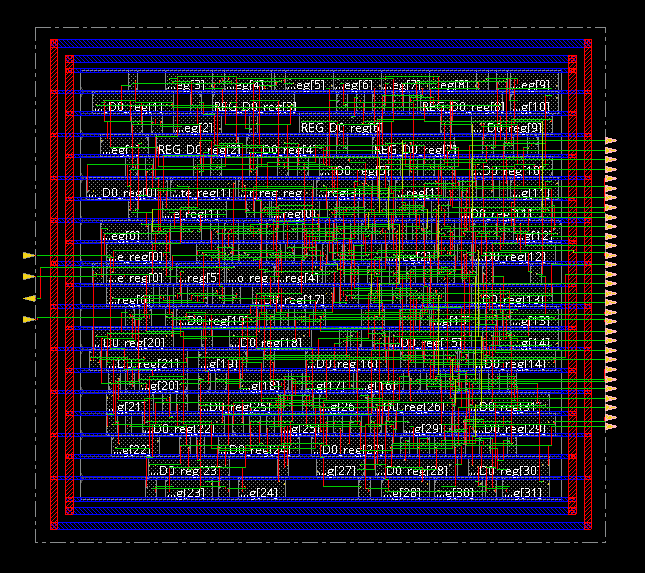

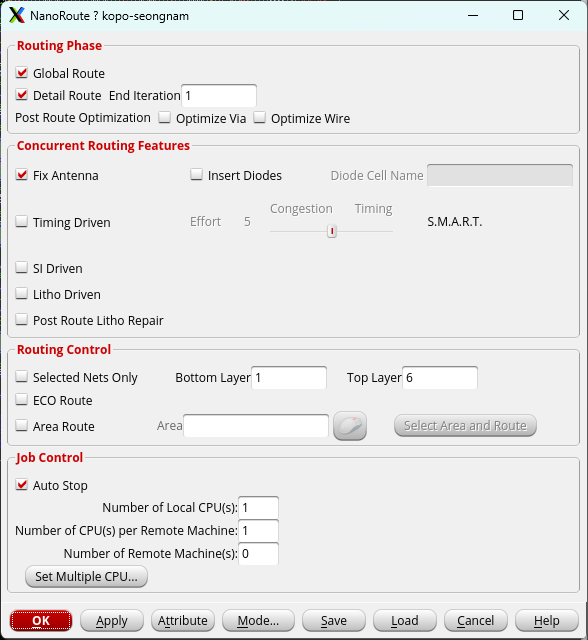

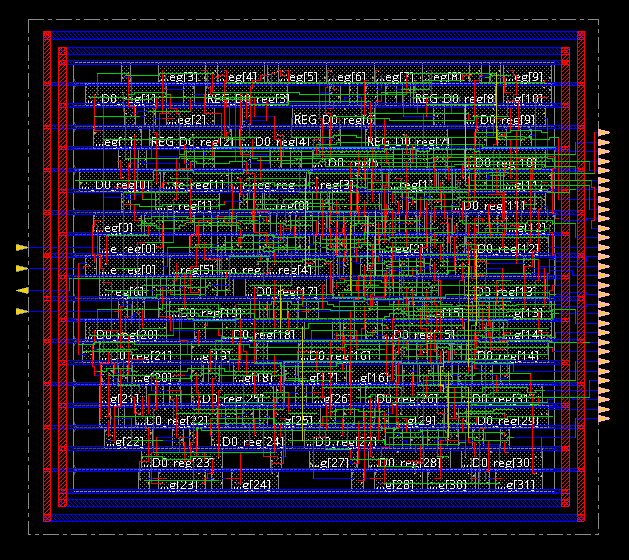

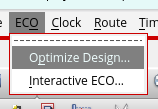

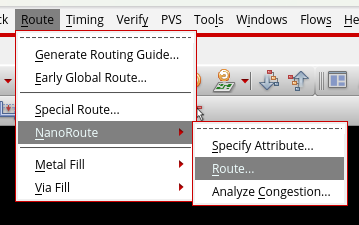

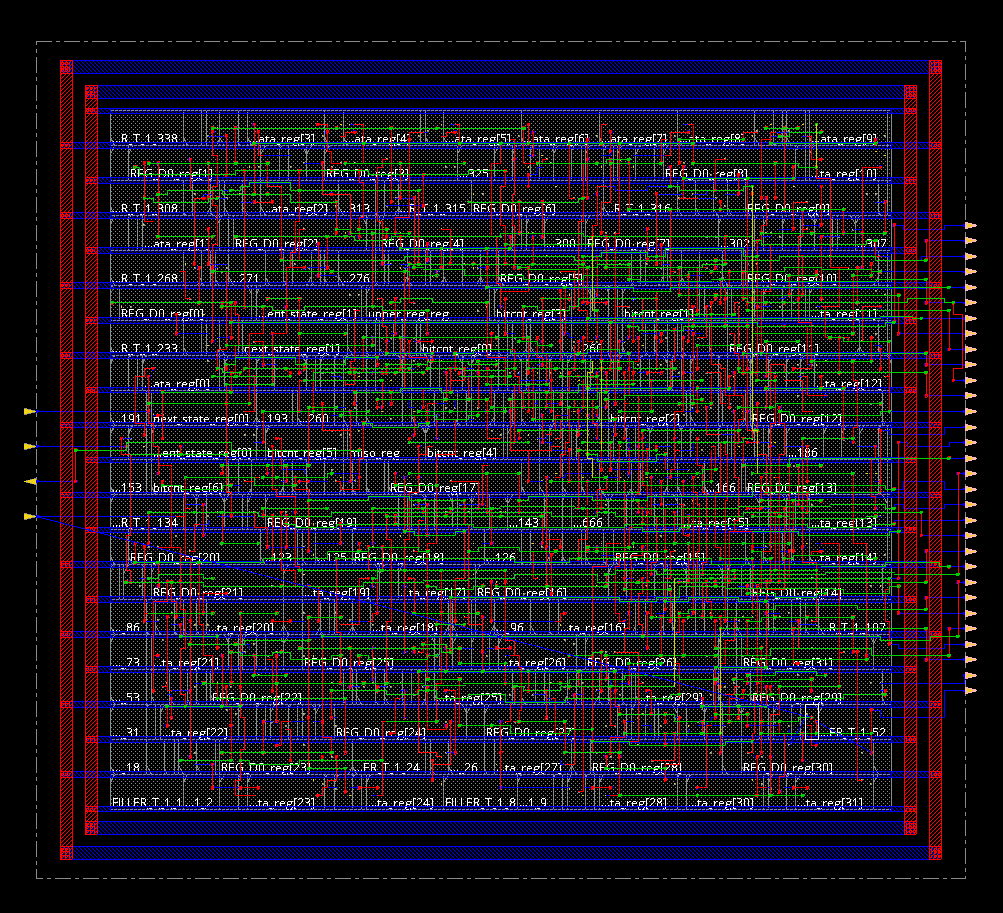

Route & Post-CTS

Route : 라우팅은 회로의 논리적인 구성 요소들을 특정한 칩 디자인에 맞게 배치하고, 신호가 흐르는 경로를 결정한다.

이 과정은 전력 소모, 신호 지연 및 전도성 등의 요소를 최적화하여 회로의 성능을 향상시킨다.

Post-CTS : Routing 이후 CTS 작업을 하는 과정이다.

Route를 통해 실제 물리적인 레이아웃으로 변환하고 난 뒤 회로가 변한 것을 확인할 수 있다.

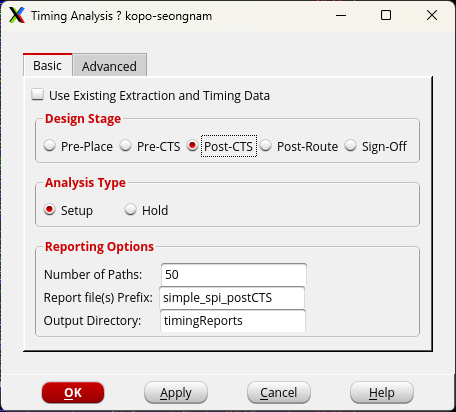

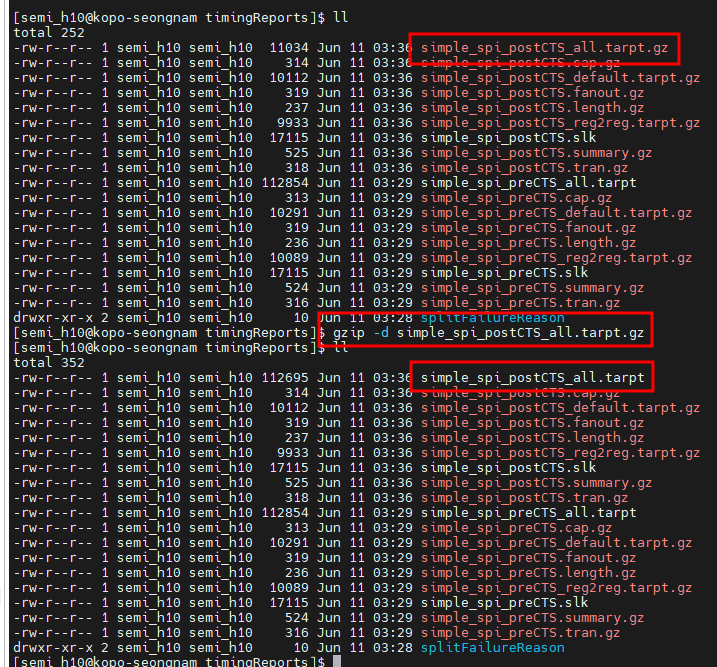

Pre-CTS와 동일하게 Post-CTS를 진행한다.

마찬가지로 Timing Report를 통해 이상이 없는지 확인한다.

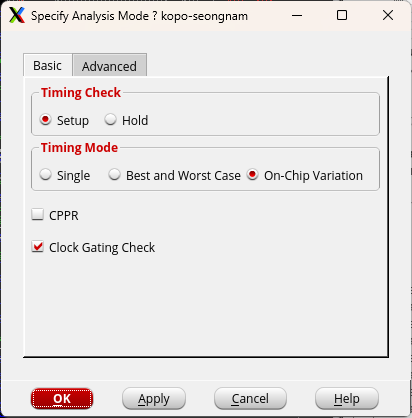

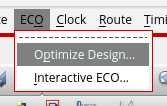

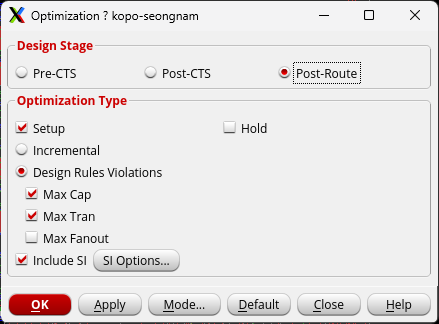

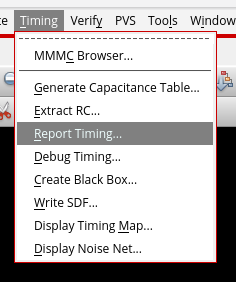

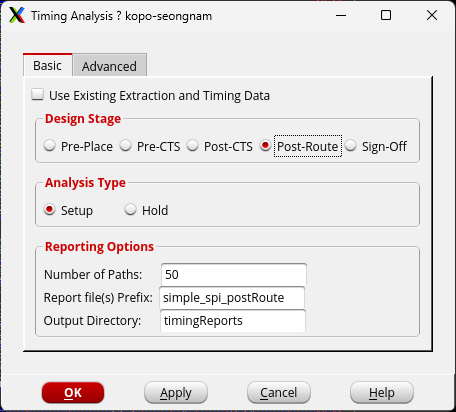

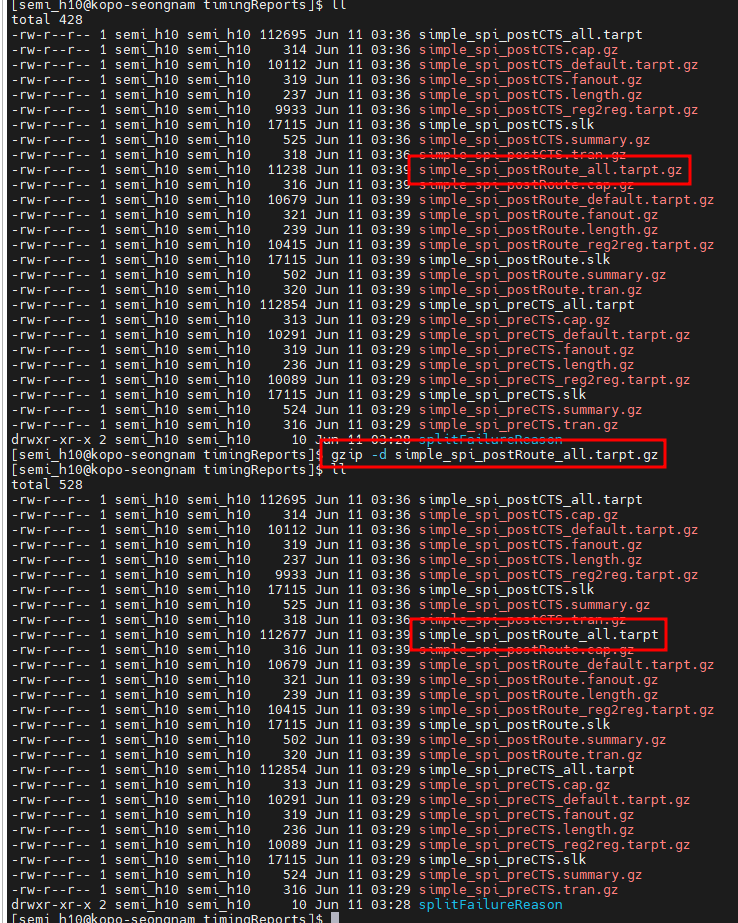

PostRoute

PostRoute는 라우팅이 완료된 후 추가적인 물리적 설계 및 분석 작업을 의미한다.

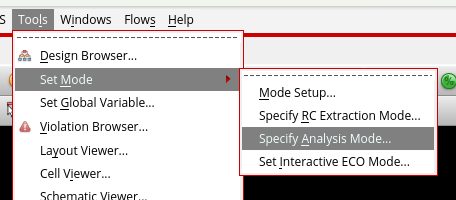

Specify Analysis Mode에서 On Chip Variation를 선택하는 것은 설계의 안정성과 신뢰성을 보장하기 위한 중요한 단계다.

따라서 OCV를 고려하여 분석을 수행하면 설계의 실제 동작을 보다 정확하게 모델링할 수 있다.

Post Route도 마찬가지로 OCV 설정 후 Routing하고, CTS를 수행하고, Timing Report를 확인하여 이상이 없는지 확인한다.

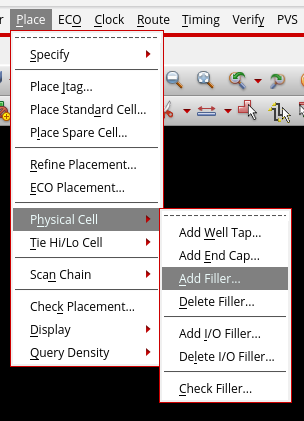

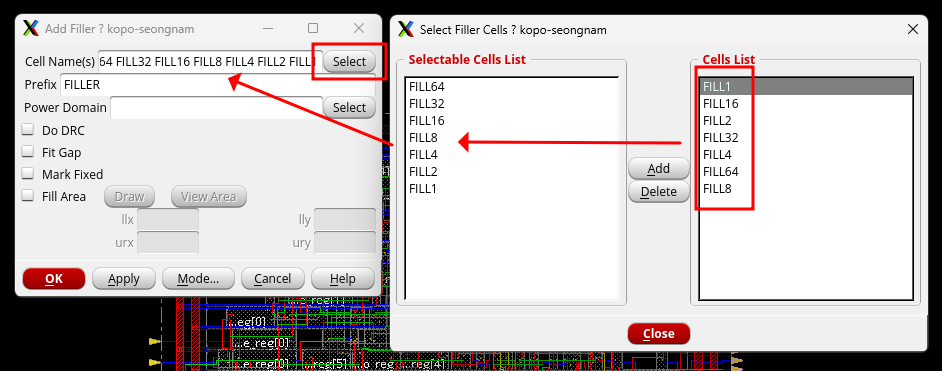

Filler

Filler는 반도체 설계에서 빈 공간을 채우는 작업을 의미한다. 빈 공간은 주로 라우팅이나 배치 과정에서 발생하며, 회로의 물리적인 레이아웃을 최적화 하는 데 사용된다.

Filler에서 Fill 뒤에 붙은 숫자들은 그만큼 큰 공간을 채우는데 사용된다.

Fill 숫자를 큰 숫자부터 해야 빈공간을 꽉꽉 채울 수 있다. 큰 숫자부터 안하면 오류가 발생할 수도 있다.

Filler를 적용시킨 뒤 위와 같이 빈공간이 꽉 찬 것을 확인할 수 있다.

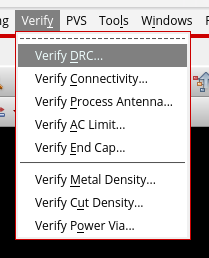

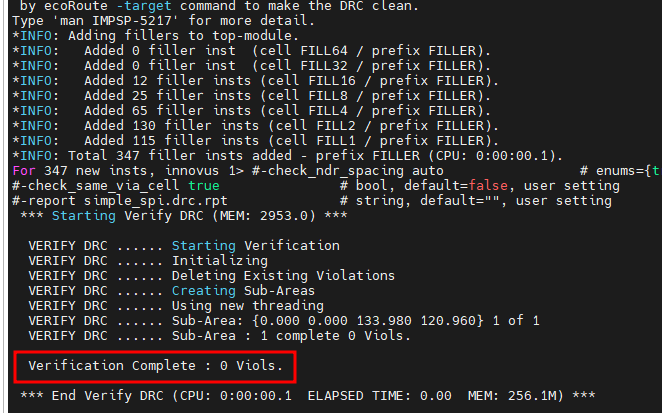

Verify

지금까지 과정에 이상이 없다면 Verify 이후 0 Viols를 확인할 수 있으며, 0 Viols가 확인되면 검사에 이상이 없는 것을 뜻한다.

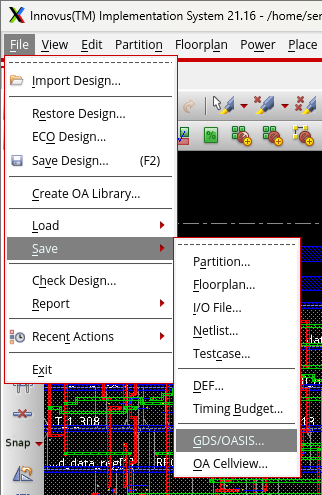

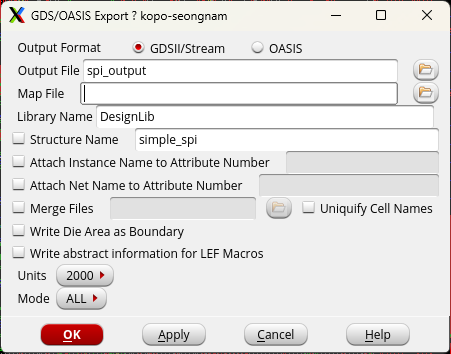

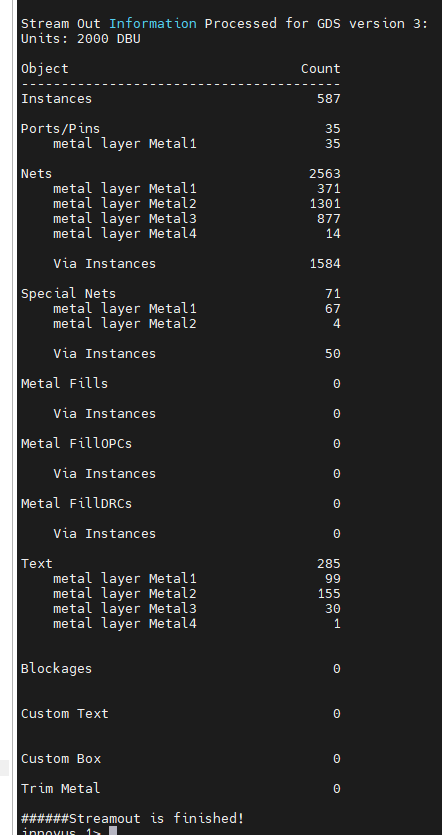

GDSII

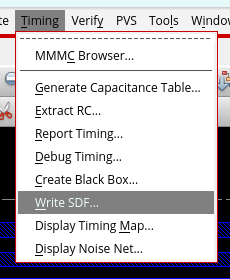

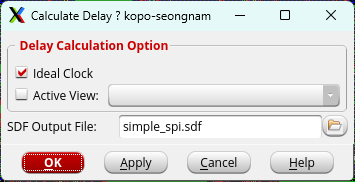

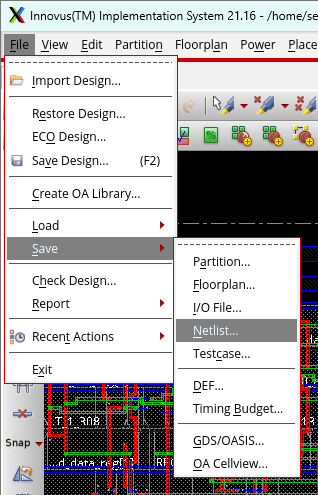

Time Violation / DRC에 문제가 없으면 GDSII을 최종적으로 저장하면 되지만 설계자에게 Post-Layout Simulation을 위한 파일을 생성하여 보내주고 Post-Layout Simulation이 이상 없으면 해당 GDSII 파일을 최종으로 넘긴다.

Post-Layout Simulation을 위한 파일

1. Netlist 파일

2. SDF 파일

P&R 이전 netlist 파일과 P&R 이후 netlist 차이점

1. P&R 이전 netlist 파일 : CTS에 대한 고려가 없다.

2. P&R 이후 netlist 파일 : CTS 진행 후 생성된 netlist

P&R 이전 SDF 파일과 P&R 이후 SDF 파일 차이점

1. P&R 이전 SDF 파일 : Cell에 대한 딜레이만 존재한다.

2. P&R 이후 SDF 파일 : Placement와 Routing이 진행되었으므로 Net Delay 정보가 포함되어 있다.

SDF 파일 출력

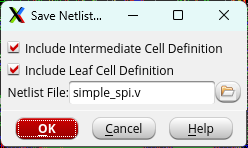

Netlist 출력

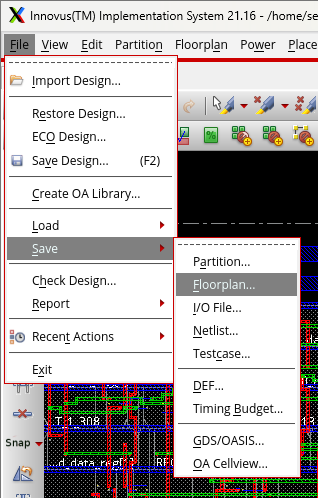

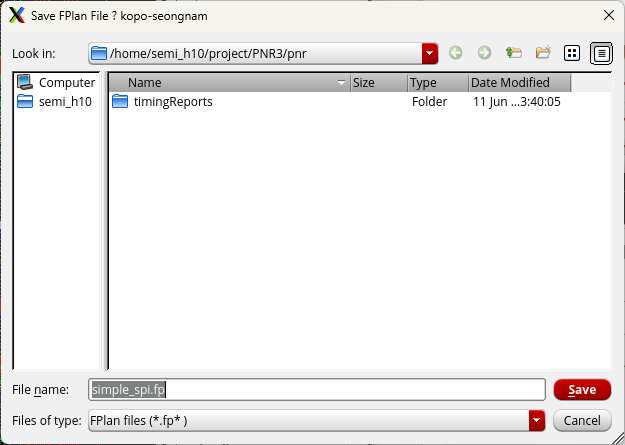

Floorplan 저장

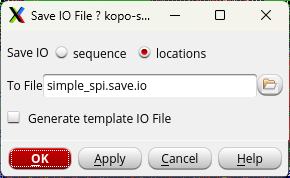

I/O 파일 저장

GDS 파일 저장

'Semiconductor > Synthesis, PnR' 카테고리의 다른 글

| Synthesis - Clock Gating (이론 및 Syn 후 Simulation 확인) (0) | 2024.09.25 |

|---|---|

| Synopsys - Synthesis 합성 (0) | 2024.04.16 |

| Cadence - Synthesis / Pre_layout Simulation (0) | 2024.04.09 |