https://insoobaik.tistory.com/666

이전 tpsram을 사용한 Cache 동작과정에 대해 알아보았다.

이번 포스팅에서는 Cache 사용되는 SRAM의 두 종류 tpsram, dpsram에 대해 알아볼 것이다.

■ Two Port SRAM

Two Port SRAM의 경우 2개의 Port를 통해 Read, Write를 할 수 있다. 각 Port는 Read, Write만 할 수 있다. Port에 대한 주소만 같지 않다면 A포트에서 값을 쓰고 B포트에서 같은 클럭에 값을 읽어갈 수 있다.

■ Dual Port SRAM

Dual Port SRAM은 마찬가지로 Read, Write 포트가 구분되어 있으며, 추가로 입출력 Port 쌍이 두개가 존재한다. Two Port의 경우 주소가 다르다 하더라도 결국 한 주소에 Read 혹은 Write밖에 할 수 없었지만 Dual Port의 경우 주소가 다르다면 Read, Write를 동시에 전부 수행할 수 있다.

■ TPSRAM, DPSRAM Code, Schematic, Simulation

- tpsram.v Code

module tpsram #(

parameter DEPTH=8,

parameter WIDTH=32,

parameter DEPTH_LOG=$clog2(DEPTH)

)(

input clk, //write clk

input we, //write enable

input [DEPTH_LOG-1:0] wa, //write addr

input [WIDTH-1:0] wd, //write data

input re, //read enable

input [DEPTH_LOG-1:0] ra, //read addr

output reg [WIDTH-1:0] rd //read data

);

reg [WIDTH-1:0] mem[DEPTH-1:0];

initial begin

for (int i=0;i<DEPTH;i++) mem[i] = 0;

end

always @(posedge clk)

if (we) mem[wa] <= wd;

always @(posedge clk)

if (re) rd <= mem[ra];

endmodule

이전에 작성한 SRAM과 구조도 비슷하며, 코드 동작 방식도 매우 유사하다.

Two Port의 경우 두개의 Port가 별도로 동작하기 때문에 Read, Write 신호에 따라 Data를 Read하고 Write 동작으로 하도록 코드가 작성되어 있다.

- tpsram Schematic

- tpsram Simulation

Simulation 확인 결과 Write Enable과 Read Enable 신호에 맞춰 Data가 Read, Write 되는 것을 확인할 수 있다.

- dpsram.v 코드

module dpsram #(

parameter DEPTH=8,

parameter WIDTH=32,

parameter DEPTH_LOG=$clog2(DEPTH)

)(

input clk,

input cs_a, we_a,

input [DEPTH_LOG-1:0] ad_a,

input [WIDTH-1:0] wd_a,

output reg [WIDTH-1:0] rd_a,

// input clk_b

input cs_b, we_b,

input [DEPTH_LOG-1:0] ad_b,

input [WIDTH-1:0] wd_b,

output reg [WIDTH-1:0] rd_b

);

reg [WIDTH-1:0] mem[DEPTH-1:0];

initial begin

for (int i=0;i<DEPTH;i++) mem[i] = 0;

end

always @(posedge clk)

if (cs_a & we_a) mem[ad_a] <= wd_a;

else if (cs_a) rd_a <= mem[ad_a];

always @(posedge clk)

if (cs_b & we_b) mem[ad_b] <= wd_b;

else if (cs_b) rd_b <= mem[ad_b];

endmodule

Dual Port는 a, b에 대해 Input, Output이 구분되어 있고, a, b 각각의 동기화 신호를 전달함으로서 총 4개의 Port를 통해 Read, Write를 할 수 있다.

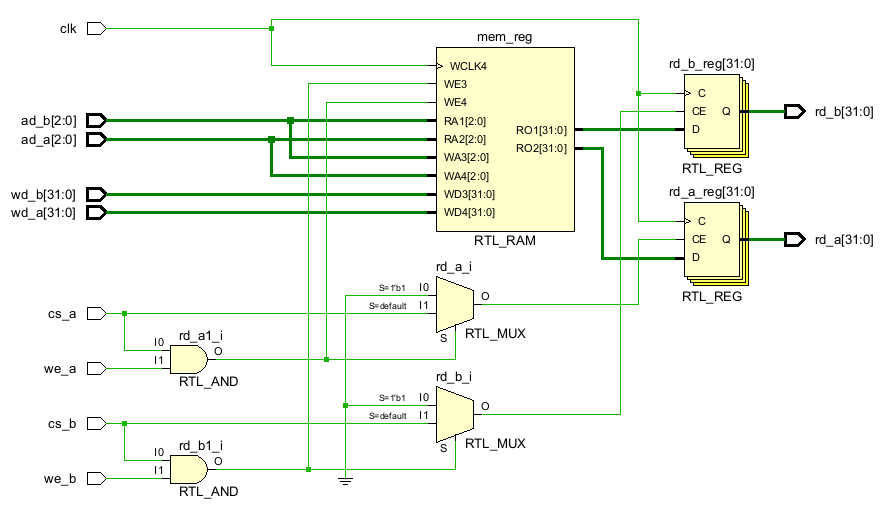

- dpsram Schematic

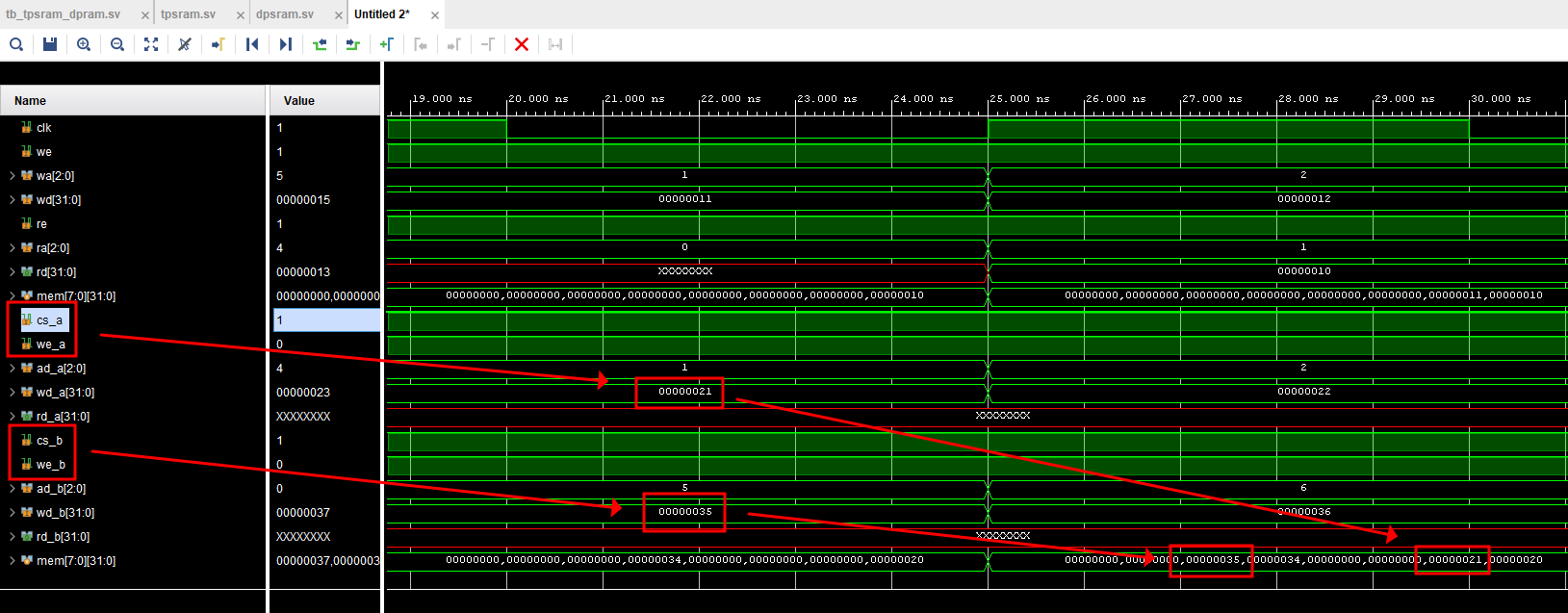

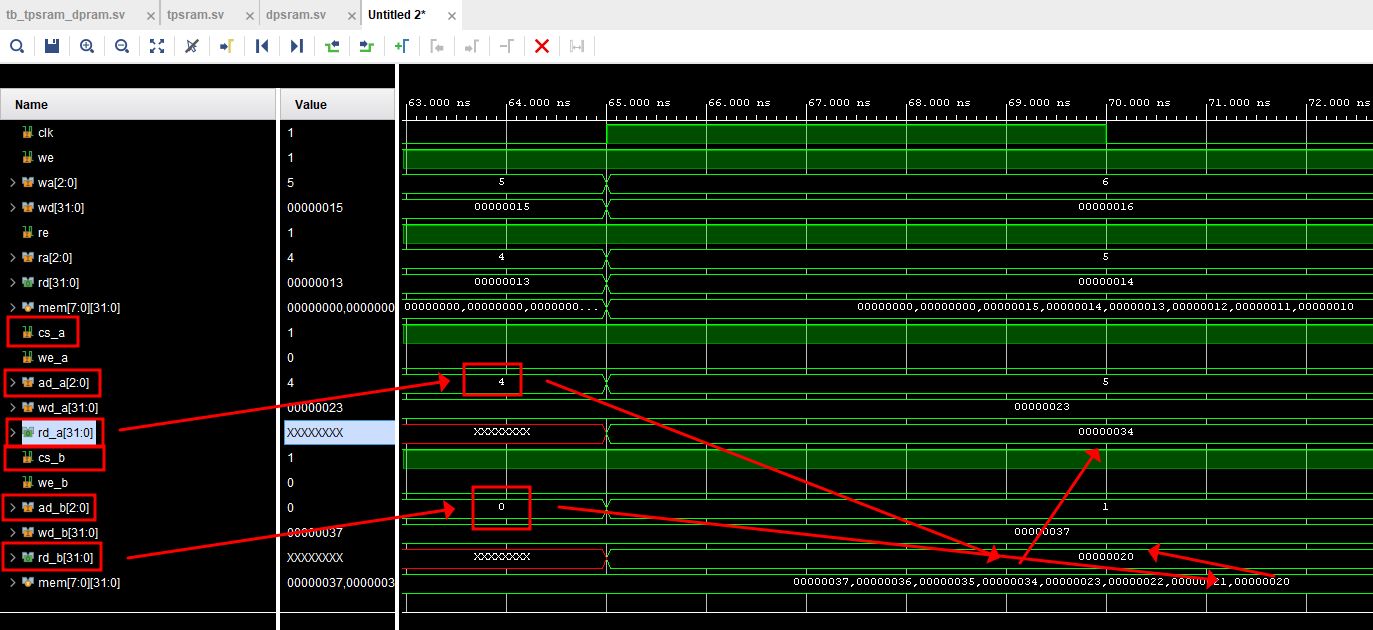

- dpsram Simulation

Dual Port SRAM의 Simulation를 보게되면

1. a, b는 각각 cs 신호에 맞춰 해당 포트가 동작하게 되어있다.

2. 기존의 Two Port SRAM과 동일하게 Write Enable 신호가 들어오면 Data를 저장한다.

3. Read의 경우 Data가 필요할 때마다 읽어오면 되고, Wrtie 중에도 Read가 가능하기 때문에 Read Enable 신호는 별도로 생성하지 않고도 Data를 바로바로 읽어올 수 있다.

(Write Enable이 필요한 이유는 Write의 경우 신호를 별도로 제어하지 않으면 쓰는 도중에 값이 중복되어 Write될 수 있기 때문이다.)

'Semiconductor > RTL, Simulation' 카테고리의 다른 글

| 컴퓨터 구조 및 CPU 동작 원리 (3) - 32 Bit RISC CPU(Pipeline) RTL 설계 (0) | 2024.10.14 |

|---|---|

| RTL - I2C (Master / Slave - Simulation, Code) (0) | 2024.08.17 |

| RTL - CACHE(Two Port SRAM) 동작 과정 및 설명 (0) | 2024.08.07 |

| RTL - SRAM (`ifdef를 이용한 FPGA, ASIC 코드 분리) (0) | 2024.08.06 |

| RTL - SPI (Master, Slave, FSM) (2) FSM, MASTER, SLAVE & SLVAE 활용 (0) | 2024.06.02 |