FIFO(First In, First Out)

먼저 들어온 데이터가 먼저 나가게 되는 데이터 처리와 관련된 자료구조에 해당한다.

위 그림과 같이 저장소에 먼저 들어온 값을 기준으로 Data가 쌓이고 Data 요청이 들어오게 되면 먼저 들어온 Data부터 나가게 된다.

Enqueue, Dequeue = Push, Pop이라고 생각하면 된다.

FIFO 사용 이유

FIFO는 일종의 Buffer처럼 사용된다.

위 그림의 왼쪽처럼 A에서 B에게 데이터를 전달해야 하는데, B가 Busy상태에 있으면 A는 다른 작업을 하지 못한채로 B가 데이터를 받을 수 있는 상태(IDLE)가 될 때까지 대기해야 한다.

하지만 우측 그림처럼 중간에 FIFO 방식의 Buffer를 생성하게 되면, A에서 B에게 전달해야 하는 데이터를 Buffer에 넣어두고 다른 작업을 실행할 수 있다.

B 또한 Busy 상태였다가 IDEL 상태가 되면 Buffer에 있는 데이터를 하나씩 받아서 처리하면 된다.

우측의 Buffer를 사용하게 되면 A, B 각자 작업을 수행하면서도 별도의 저장소를 통해 상대방의 상태에 영향을 덜 받게 되고 병목 현상을 줄이게 된다.

아래 자세히 설명하겠지만 무작정 A에서 B한테 전달할 Data를 Buffer 전달하면 안된다.

예를들어 Buffer에 Data가 가득 차 있는 상태에서 A에서 Buffer로 데이터를 추가로 전달하게 되면 해당 데이터는 손실되게 된다.

이런 상황을 방지하기 위해 Buffer가 꽉 차기 전에 A에게 신호를 전달하여 Buffer에 Data를 전달하지 말라는 신호를 보내야 한다.

이렇게 특정 Flag를 설정해야 A에서 Buffer에 데이터를 보내도 될 때와 보내면 안될 때를 구분해줘야 한다.

FIFO Interface

기본적으로 FIFO Buffer도 일종의 저장소이기 때문에 Data를 저장하는 공간이 필요하다.

| AF_LEVEL | Almost Full Level로 Data가 거의 다 찼기 때문에 Data 전달에 주의해야 한다는 의미다. |

| AE_LEVEL | Almost Empty Level로 Data를 보내도 된다는 의미를 가진다. |

| clk | Clock |

| rstn | reset negative |

| push | FIFO Buffer에 Data를 넣는 행위를 의미한다. |

| pop | FIFO Buffer에서 Data를 꺼내는 행위를 의미한다. |

| din | Data Write |

| dout | Data Read |

| full | Buffer가 꽉차서 더이상 Data를 쓸 수 없는 상태를 의미한다. |

| empty | Buffer에 Data가 없어서 읽을 수 없는 상태를 의미한다. |

| almost_full | 거의 다 찼다는 의미 (AF_LEVEL) |

| almost_empty | 거의 비었다는 의미 (AE_LEVEL) |

FIFO 동작 과정

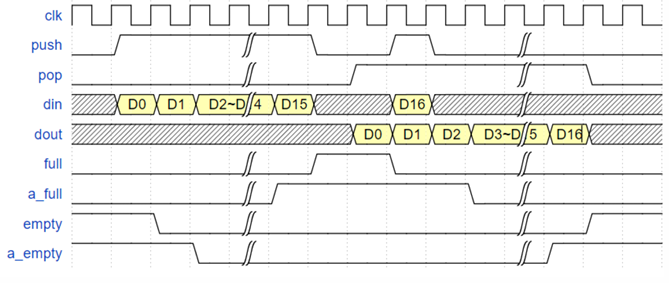

현재 FIFO Buffer의 크기가 16bit 크기를 가지고 있다.

push,와 pop 신호가 High 일 때 Data를 하나씩 넣고 빼는 동작을 수행하게 된다.

push 신호가 High일 때 Data를 계속 push하다가 15개의 Data가 들어가면 a_ful 신호를 High로 전달하고, 16개의 Data가 들어가는 순간 full 신호를 High 신호로 변경한다. full 신호가 High가 되면 Data를 전달할 수 없게 된다.

이후 pop 신호가 High가 되면 처음 들어온 D0 Data부터 전달하게 된다.

처음 pop을 통해 Data를 전달하게 되면 Buffer에 자리가 생기기 때문에 이때부터 다시 push를 통해 Buffer에 Data를 전달할 수 있다.

empty 신호도 full과 반대로 Buffer에 Data가 비어있거나 거의 비어있을 때 High 신호를 전달하게 된다.

- Synchronous

Synchronous

위 그림처럼 FIFO가 하나의 Clock에 대해 동기화되어 Data를 주고 받게 된다면 시스템 전체의 성능이 Clock 주파수에 따라 결정되어버린다. 그 외 Clock이 동기화 될 경우 타이밍에 대한 데이터 처리 제약이 높아질 수 밖에 없다.

또 SoC는 기본적으로 내부에 여러 Clock Domain이 사용되기 때문에 현실적으로 동기식 FIFO만으로 이러한 환경을 지원하기가 쉽지 않다.

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| AMBA - AMBA 이론편 (0) | 2024.09.04 |

|---|---|

| FIFO - Asynchronous, CDC, Metastability, Synchronizer, GrayCounter (2) (0) | 2024.08.22 |

| CPU 구조 및 동작 원리 (RISC, Pipeline, Hazard) (2) (1) | 2024.08.15 |

| I2C 구조 및 동작 원리 (0) | 2024.08.14 |

| CPU 구조 및 동작 원리 (1) (0) | 2024.08.13 |