AMBA

AMBA (Advanced Microcontroller Bus Architecture) ARM에서 개발한 오픈 표준 Interconnect

SoC 설계에서 프로세서, 메모리, 주변 장치 간의 통신을 효율적으로 관리하기 위해 사용된다.

AMBA는 SoC 설계에서 다양한 IP Core를 연결하는 데 널리 사용된다.

Bus

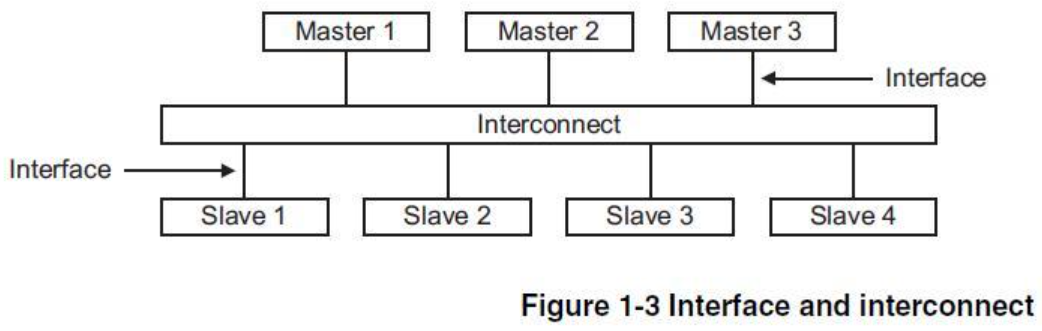

Bus는 여러 Block들이 Data를 서로 주고 받기 위해 전기적으로 연결한 공유 신호선이다.

Bus는 각 IP들을 이어주는 역할을 한다.

1. Interface의 간소화

Data를 주고 받는 여러개의 IP Block들을 서로 Point to Point로 연결하게 되면 선이 무수히 많아지며, Bus를 사용하면 이를 해결할 수 있다.

2. 확장성

IP Block을 추가해도 Bus에만 선을 연결하면 되기 때문에 확장성에 용이하다.

위 그림처럼 구성은 간단해 보이지만 무작정 하나의 Bus에 IP Block들을 연결해서는 안된다.

각 IP Block들은 Bus를 통해 통신할때 정해진 규칙이 있어야 하며 그 규칙을 따라야 한다. 이를 "프로토콜(Protocol)"라 부른다.

(도로에서 운전하기 위해선 초록불에 출발하고, 빨간불에 멈춰야하는 규칙처럼 말이다.)

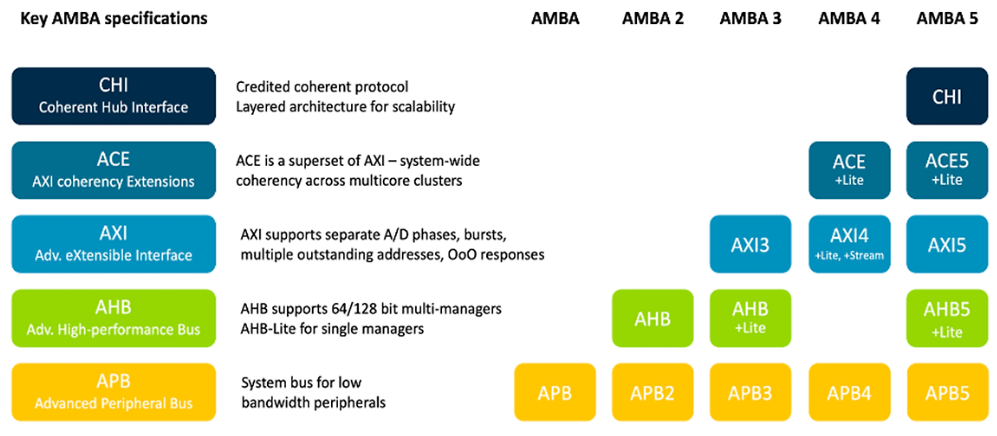

위 그림은 ARM사에서 제공하는 BUS의 종류다.

APB부터 CHI까지 총 5가지의 Bus 아키텍처가 존재한다.

각 Bus 아키텍처가 지원할 수 있는 퍼포먼스가 다르기 때문에 각 용도에 맞게 사용하면 된다.

APB, AHB, AXI를 주로 다루겠다.

이 3가지 중 AXI > AHB > APB의 퍼포먼스를 가지게 된다.

Bus 아키텍처가 나뉘어져 있는 이유를 자세히 설명하자면 각 장치들의 처리 속도가 전부 다르기 때문이다.

CPU와 DRAM을 예시로 들겠다.

CPU의 경우 처리 속도가 매우 빠르고 DRAM의 경우 상대적으로 처리 속도가 느리다.

CPU와 DRAM을 AHB Bus를 공통으로 사용하게 되면 CPU 입장에선 처리 속도에 비해 처리하는 양이 매우 적기 때문에 최상의 퍼포먼스를 보여줄 수 없다.

반대로 CPU와 DRAM을 처리 속도가 빠른 Bus에 연결해도 DRAM은 Bus의 처리 속도를 따라가지 못하기 때문에 Bus가 기다려야하기 때문에 무작정 좋은 Bus만 사용하는 것은 좋은 방법이 아니다.

그렇기 때문에 위 사진과 같이 각 장치의 처리 속도에 맞는 Bus를 사용하는 것이 가장 좋은 방법이다.

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| WaveDrom (Timing Diagram) 사용 법 (0) | 2024.09.19 |

|---|---|

| AMBA - AXI 이론편 (0) | 2024.09.04 |

| FIFO - Asynchronous, CDC, Metastability, Synchronizer, GrayCounter (2) (0) | 2024.08.22 |

| FIFO - 구조 및 동작 원리 (1) (0) | 2024.08.20 |

| CPU 구조 및 동작 원리 (RISC, Pipeline, Hazard) (2) (1) | 2024.08.15 |