AXI

AXI(Advanced eXtensible Interface) ARM에서 개발한 AMBA(Advanced Microcontroller Bus Architecture) Bus Protocol의 일부로 High Performance 및 High Band Width 시스템에서 사용되는 Interface다

AXI Bus는 Write Address / Data, Read Address / Data, Response 총 5개의 Channel로 분리가 되어 있어서 Read와 Write가 동시에 가능하다.

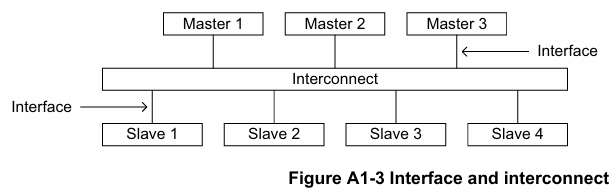

AXI Architecture

Channel

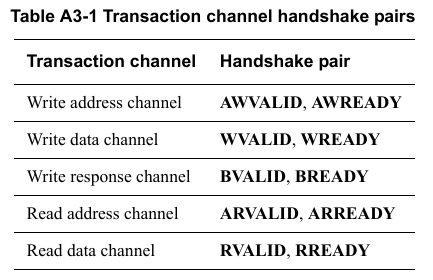

Channel은 총 5개의 Channel이 있다.

1. Write Address Channel

2. Write Data Channel

3. Write Response Channel

4. Read Address Channel

5. Read Data Channel

AXI Spec을 보게되면

Read : Read Address Channel, Read Data Channel

Write : Write Address Channel, Write Data Channel, Write Response Channel

총 5개의 독립적인 Channel이 존재한다.

Channel들을 통해 Address나 Data가 전달될 때 각 Channel에 존재하는 VALID와 READY Signal을 이용해 HankShake 과정을 거치게 된다.

VALID : 보내는 쪽에서 보낼 준비가 됐다라는 Signal

READY : 받는 쪽에서 받을 준비가 됐다라는 Signal

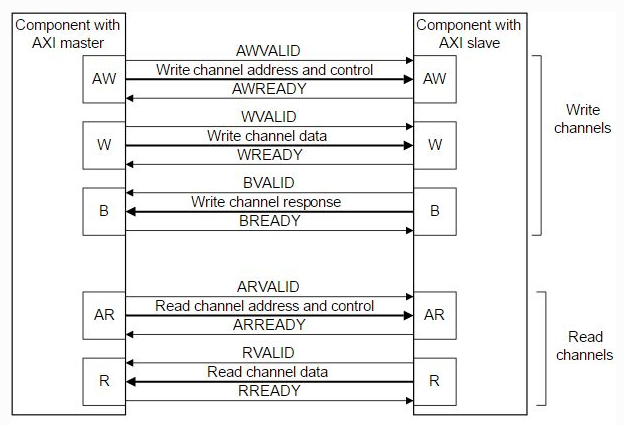

AXI HandShake

1. Master가 Write 할 때

Address - Write Address Channel

Data - Write Data Channel을 통해 Slave로 전달하고,

Slave는 Write 여부를 Write Response Channel을 통해 Mater에게 전달한다.

2. Master가 Read 할 때

Address - Read Address Channel

Data - Wriete Data Channel을 통해 Slave에 있는 Data를 읽는다.

Data를 읽을 때는 별도의 Slave의 응답을 받을 필요가 없는 것을 확인할 수 있다.

이 외에도 AXI HandShake를 위한 Signal이 많지만 추후에 자세히 다뤄보도록 하겠다.

AXI Transfer

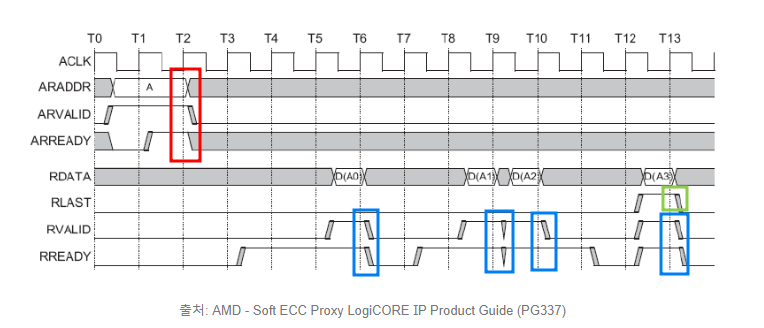

Read

기본적으로

(빨간색) ARVALID와 ARREADY가 HIGH일 때 Read Address Channel에서 HandShake가 일어나 Address가 전송된다.

(파란색) RVALID와 RREADY가 HIGH가 될 때 Read Data Channel에서 HandShake가 일어나 Data가 전송된다.

(초록색) RLAST는 Transfer가 완료될 때 HIGH가 되어 Transfer가 완료되었음을 알려주는 Signal에 해당한다.

- Read Address 전송 과정

1. Master가 ARADDR에 주소를 출력하고, 신호를 보낼 준비가 완료되면 ARVALID를 HIGH로 설정한다.

2. Slave가 신호를 받을 준비가 완료되면 ARREADY를 HIGH로 설정한다.

3. T2에서 한번의 Beat가 끝나게 되어 Read Address를 전송 후 Master는 ARVALID를 Slave는 ARREADY를 LOW로 설정한다.

- Read Data(A0) 전송 과정

1. T4에서 Slave는 Read Data를 받을 준비가 완료되어 RREADY 값이 HIGH, Master는 Read Data를 보낼 준비가 되지 않아 RVALID가 LOW이기 때문에 Data를 전송하지 않는다.

2. T5~T6에서 Master가 Read Data를 받을 준비가 완료되어 RDATA에 데이터를 출력하고, RVALID를 HIGH로 설정한다.

3. T6에서 한번의 Beat가 끝나게 되어 D(A0)가 전송된 뒤 Master는 RVALID를, Slave는 RREADY를 LOW로 설정한다.

추가적으로 Address가 주어지면 Burst Type에 따라 읽히는 주소의 값이 달리게 된다.

(위 그림은 기본적으로 Incrementing Burst Type이 사용되어 순차적으로 주소의 값이 읽혀지는 상황이다.)

(Burst Type에 대해서는 추후에 다루도록 하겠다. 궁금하다면 별도로 찾아보길 바란다.)

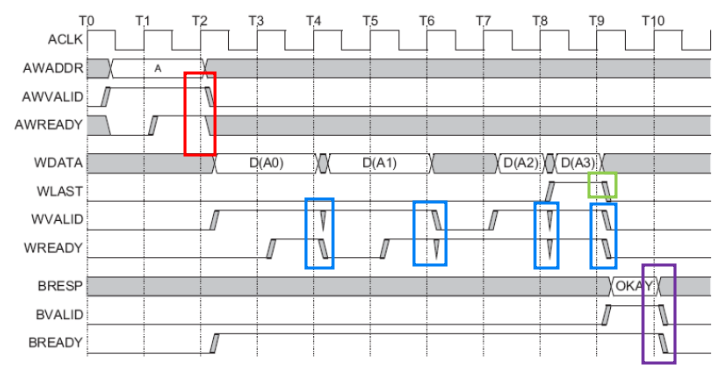

Write

Write Transfer도 Read Transfer 과정과 유사하다.

- Write Address 전송 과정

1. Master가 AWADDR에 주소를 출력하고, 신호를 보낼 준비가 완료되어 AWVALID를 HIGH로 설정한다.

2. Slave가 신호를 받을 준비가 완료되면 AWREADY를 HIGH로 설정한다.

3. T2에서 한번의 Beat가 끝나게 되어 Write Address를 전송 후 Master는 AWVALID를, Slave는 AWREADY를 LOW로 설정한다.

- Write Data(A0) 전송 과정

1. T3 Edge HIGH에서 Master는 Write Data를 보낼 준비가 완료되어 WDATA에 Write Data를 출력하고 WVALID 값이 HIGH, Slave는 Wrtie Data를 받을 준비가 되지 않아 WVALID가 LOW이므로 데이터를 전송하지 않는다.

2. T4 Edge HIGH에서 Slave가 Write Data를 받을 준비가 되어 WREADY를 HIGH로 설정한다.

3. T4에서 한번의 Beat가 끝나게 되어 Write Data 전송 후 Master는 WVALID를, Slave는 WREADY를 LOW로 설정한다.

- Response 전송 과정

1. Master에서는 T2~T3부터 Response를 받을 준비가 되어 BREADY를 HIGH로 설정

2. Write Data 전송이 완료된 뒤 T9~T10에서 Slave가 Response를 보낼 준비가 되어 BVALID를 HIGH로 설정하고 BRESP에 Response 신호를 출력한다.

3. T10에서 한번의 Beat가 끝나게 되어 Response 전송 후 Master는 BREADY를, Slave는 BVALID를 LOW로 설정한다.

(* BVALID가 HIGH가 되는 기준은 Burst Type에 의한 것이다 위 그림은 Burst가 4 beat인 것을 짐작할 수 있다.)

'Semiconductor > Digital, Analog, 회로 이론' 카테고리의 다른 글

| AXI4-Lite Interface에 대하여 (+ Template Code) (0) | 2024.09.26 |

|---|---|

| WaveDrom (Timing Diagram) 사용 법 (0) | 2024.09.19 |

| AMBA - AMBA 이론편 (0) | 2024.09.04 |

| FIFO - Asynchronous, CDC, Metastability, Synchronizer, GrayCounter (2) (0) | 2024.08.22 |

| FIFO - 구조 및 동작 원리 (1) (0) | 2024.08.20 |