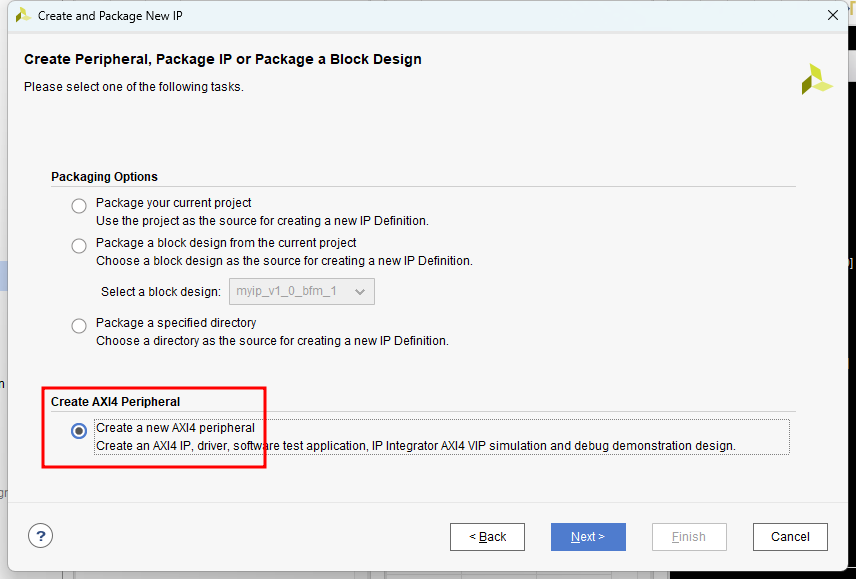

Vivado를 이용하여 AXI4-Lite Interface를 사용할 수 있다. https://insoobaik.tistory.com/689기본적은 AXI Interface에 대해서는 이전 글에서 다루어 보았다. 간단하게 요약하자면1. AXI Interface는 5개의 채널이 존재한다. (Write Address, Write Data, Response, Read Address, Read)2. 각 채널은 전부 Valid, Ready Signal에 의해 동작하게 된다. (Valid와 Ready가 전부 1이여야 동작하게 된다.) AXI4-Lite 생성위와 같이 Vivado에서 AXI4 Interface를 사용하는 IP를 생성할 수 있다. 위와 같이 AXI Interface IP에 대한 Data Width, Re..