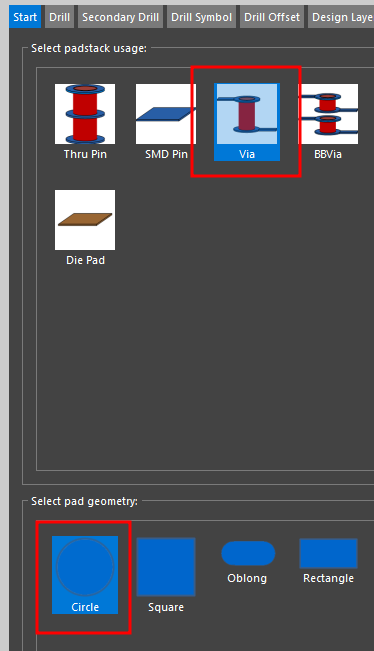

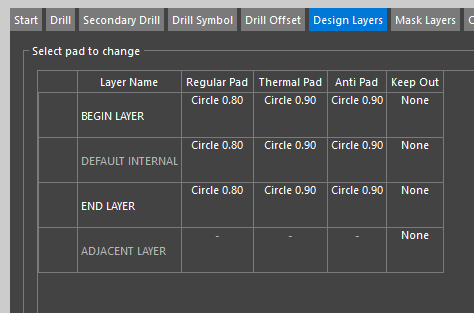

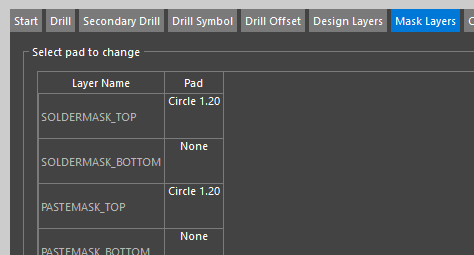

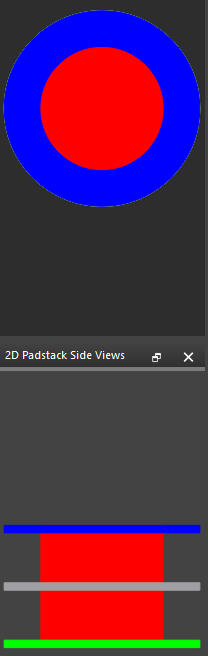

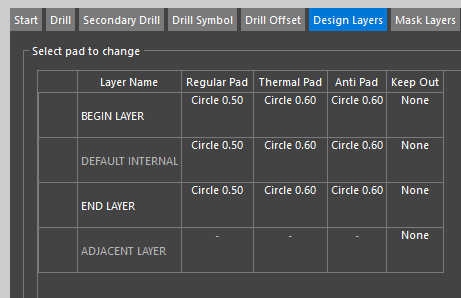

Via Pad

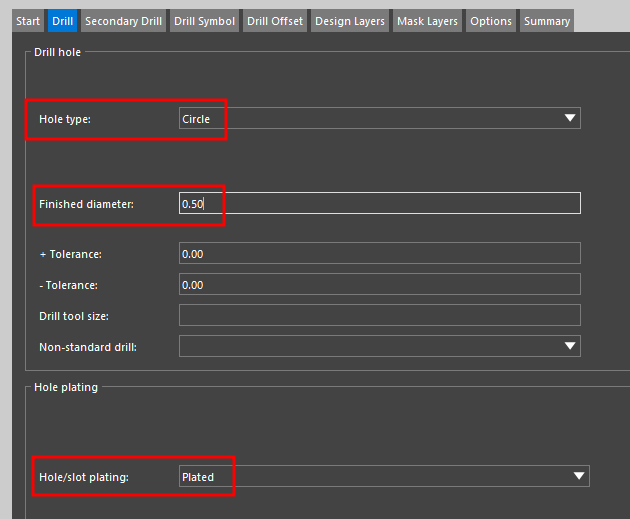

전원네트의 Via Hole / Via Pad : 0.5mm / 0.8mm

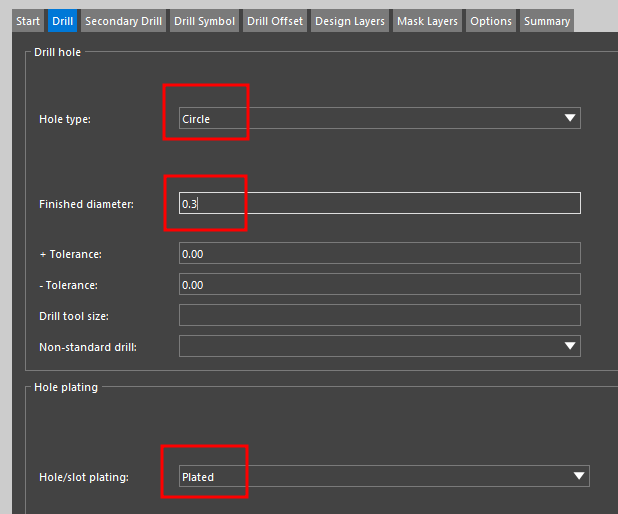

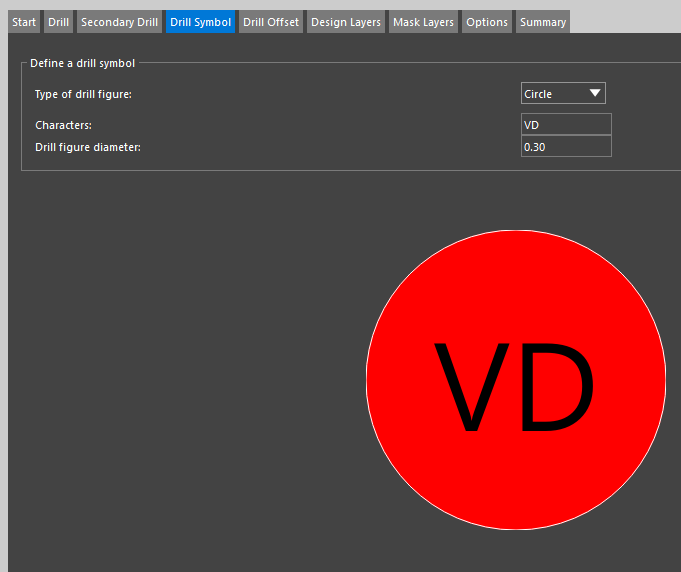

그 외 네트의 Via Hole / Via Pad : 0.3mm / 0.5mm

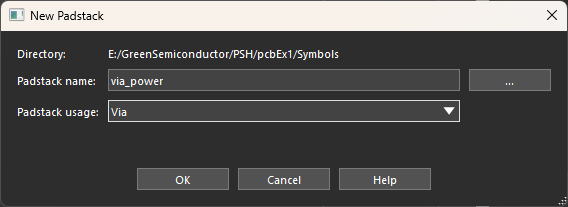

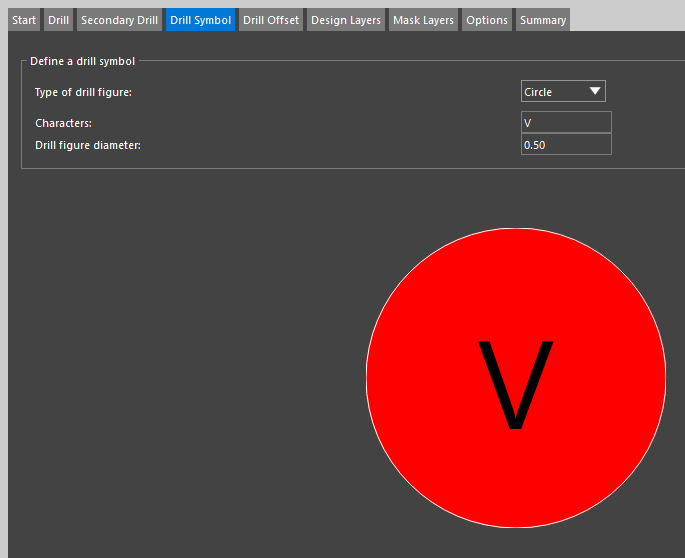

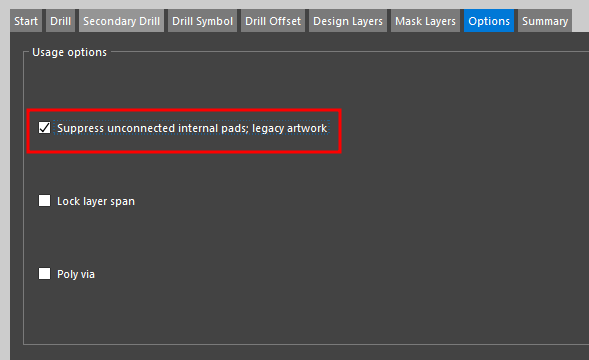

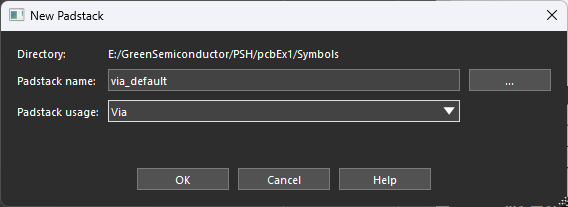

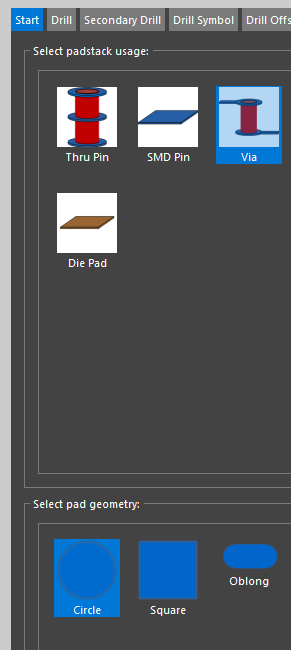

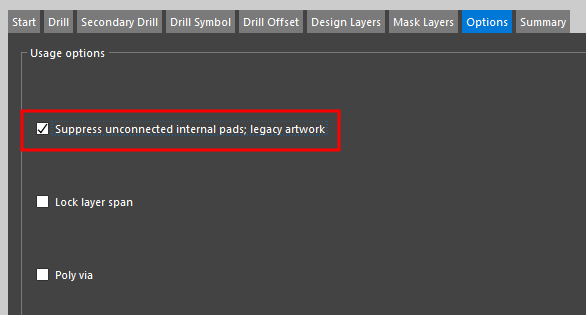

Routing 작업을 위한 via_power pad 생성

Routing 작업을 위한 via 생성

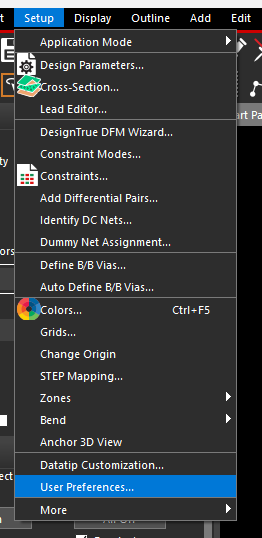

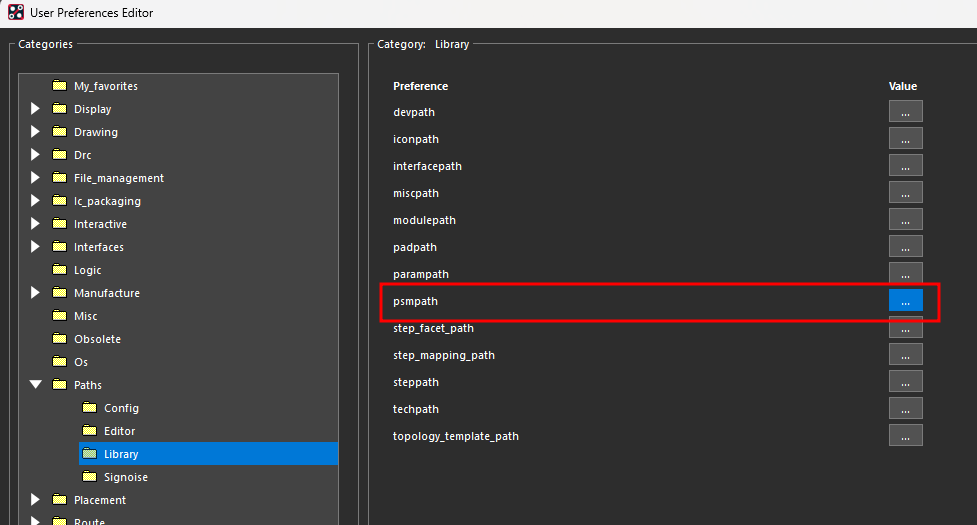

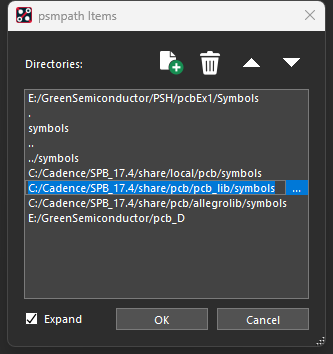

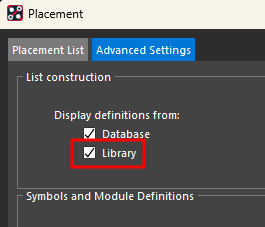

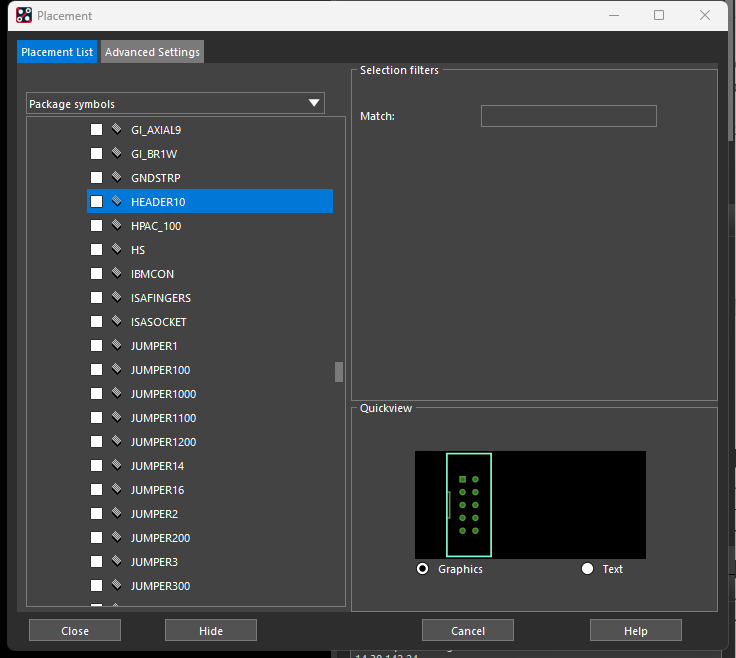

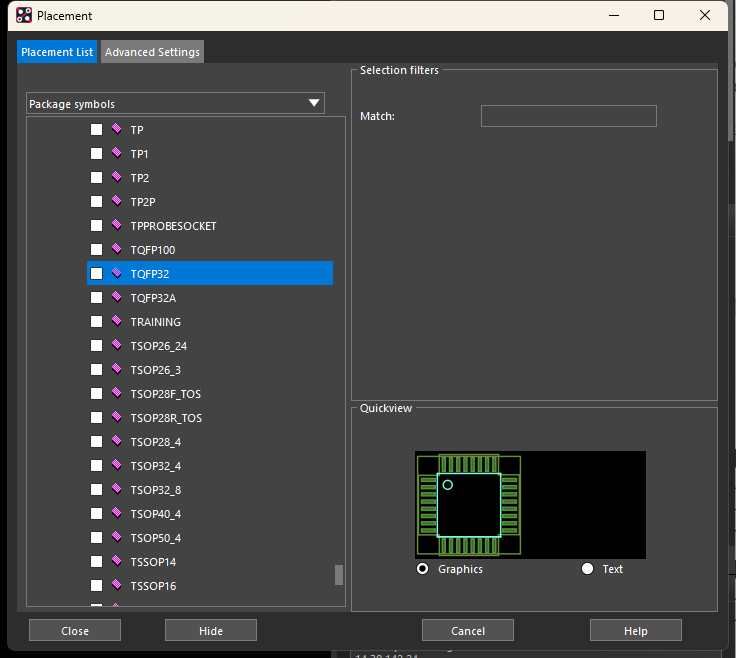

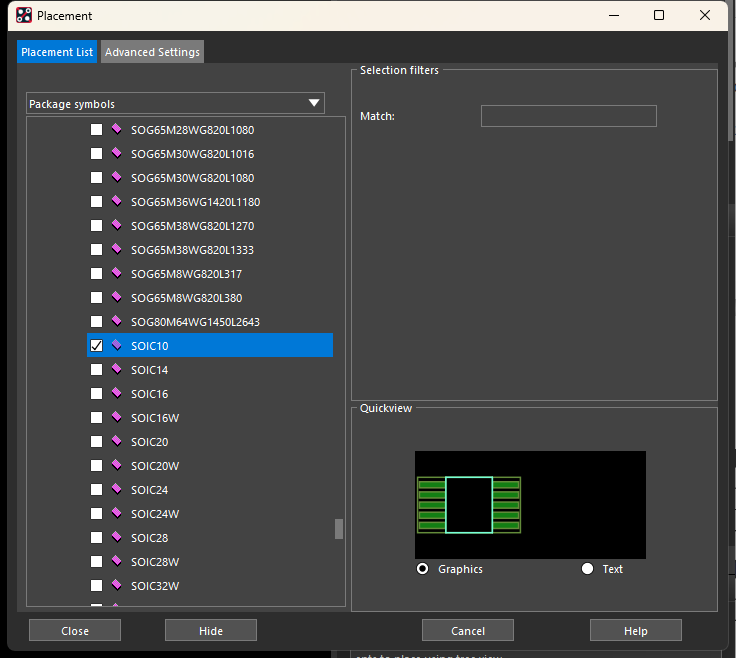

Footprint 확인

C:/Cadence/SPB_17.4/share/pcb/pcb_lib/symbols해당 경로에 .dra 즉 Footprint 파일들이 저장되어 있고 Package symbols를 통해 Footprint를 확인할 수 있는 경로다.

위와 같이 이전에 생성한 FootPrint 들이 생성되어 있는 것을 확인 할 수 있다.

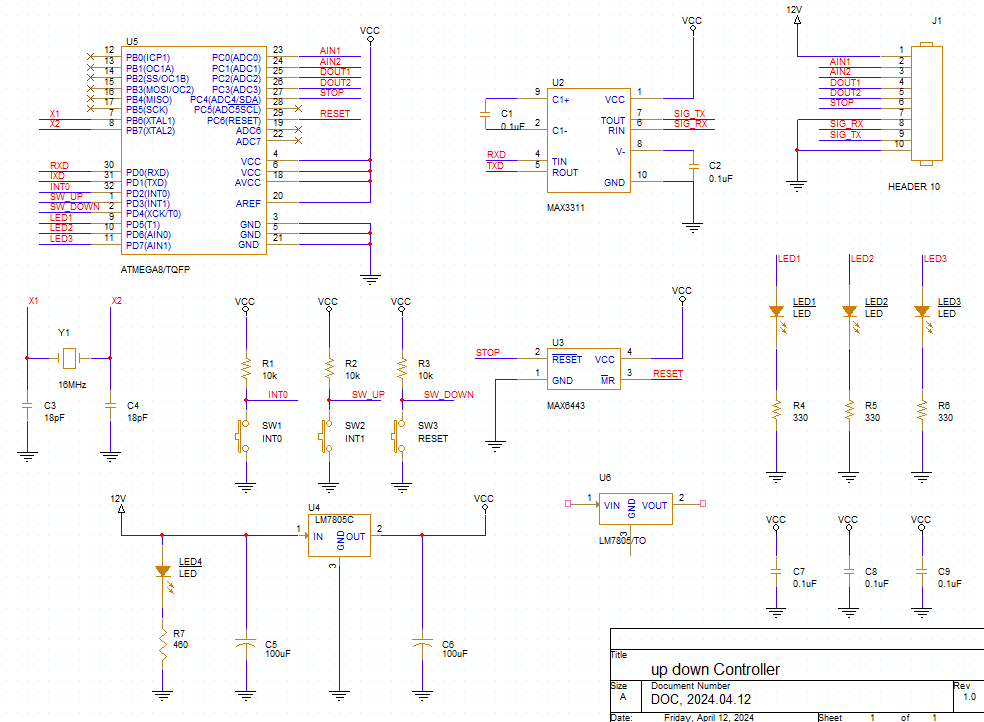

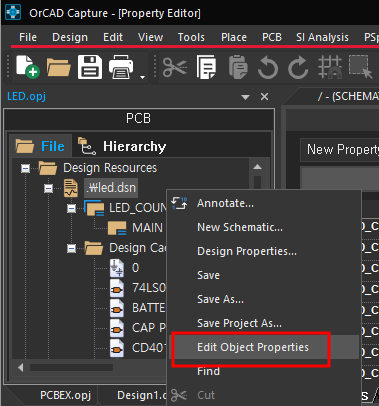

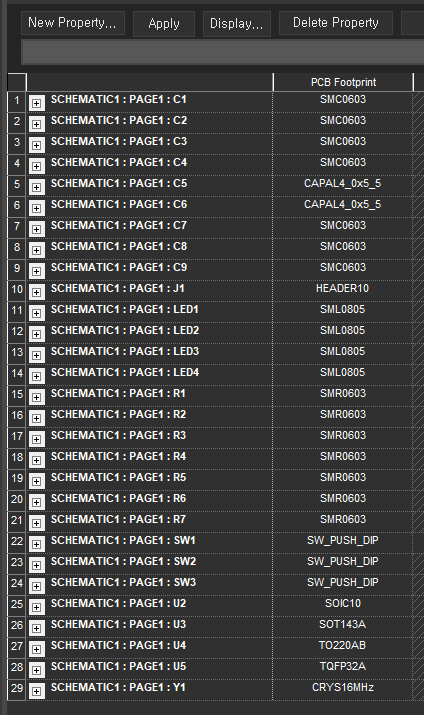

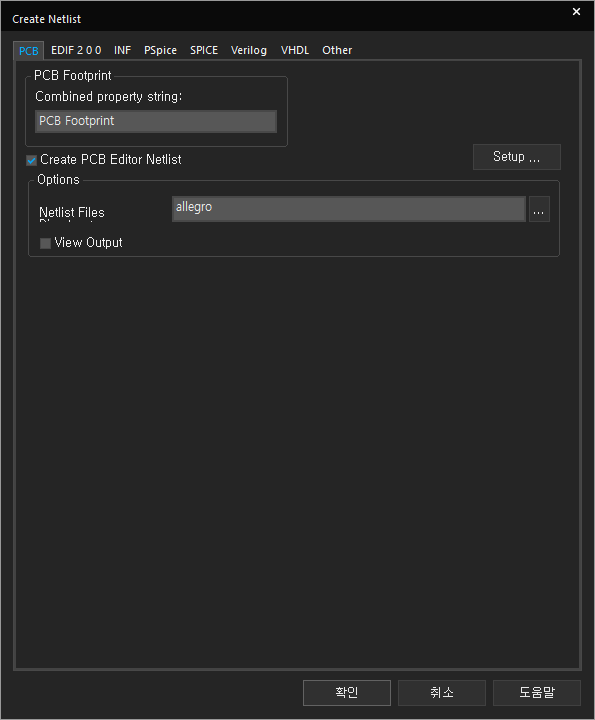

PCB Footprint 설정

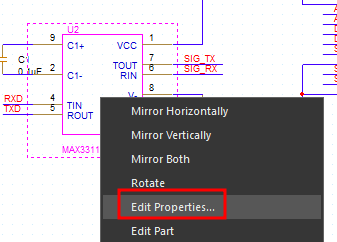

capture CIS에서 작업한다. (이전에 작업한 Capture CIS 파일을 Open 한다.)

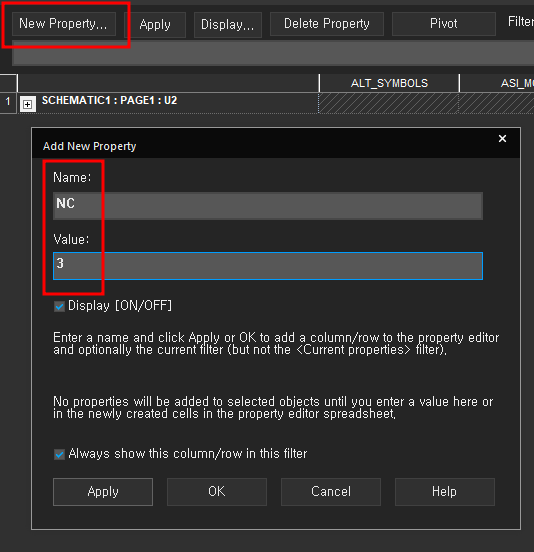

Part의 No Connect 설정

부품보다 많은 핀을 가진 부품들의 경우 Netlist 단계에서 에러가 발생하기 때문에 No Connect(NC) 처리를 해야 한다.

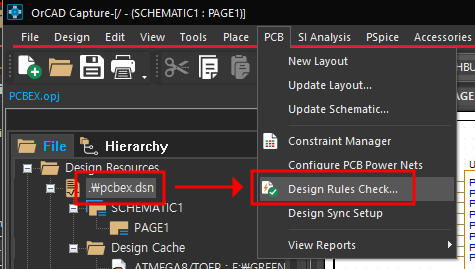

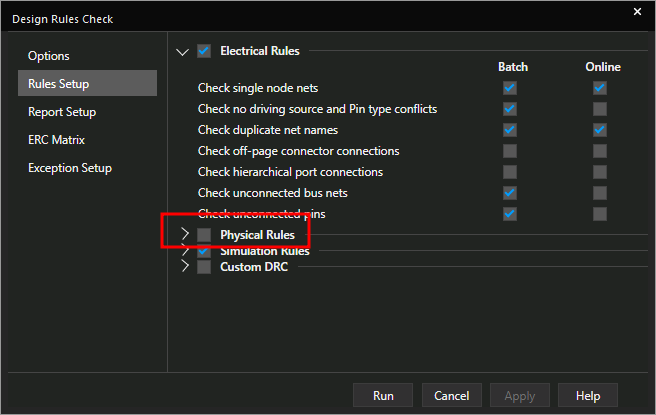

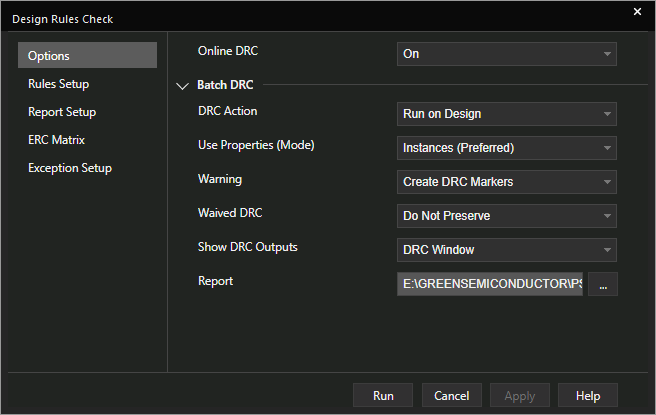

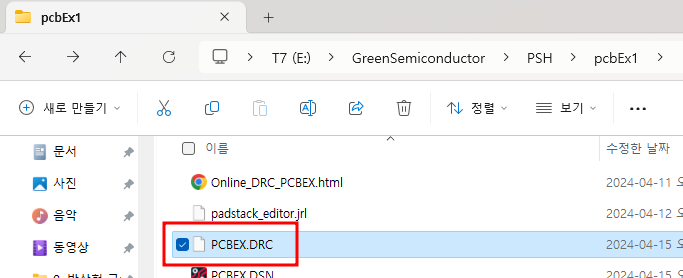

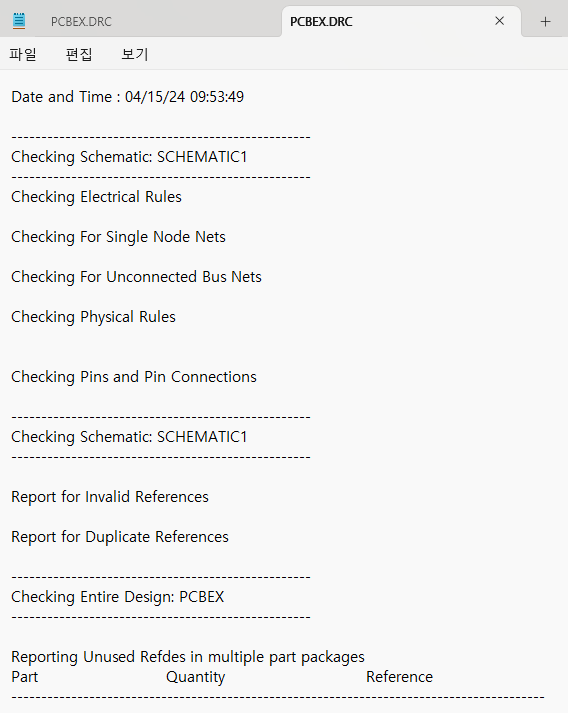

Design Rule Check

위와 같이 DRC 오류가 없으면 된 것이다.

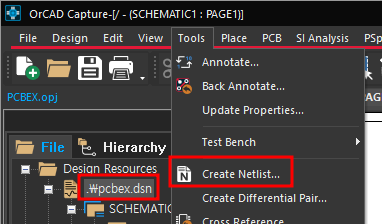

Netlist 생성

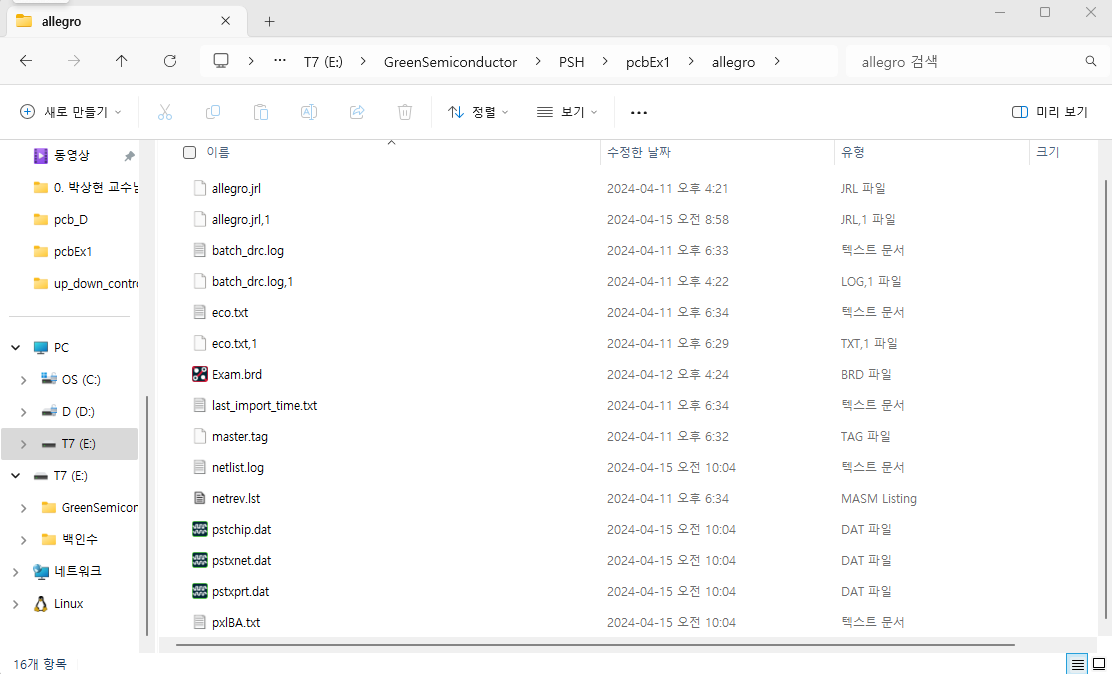

작업중인 폴더 아래 allegro라는 폴더 아래 Netlist가 생성된 것을 확인할 수 있다.

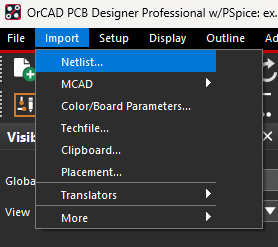

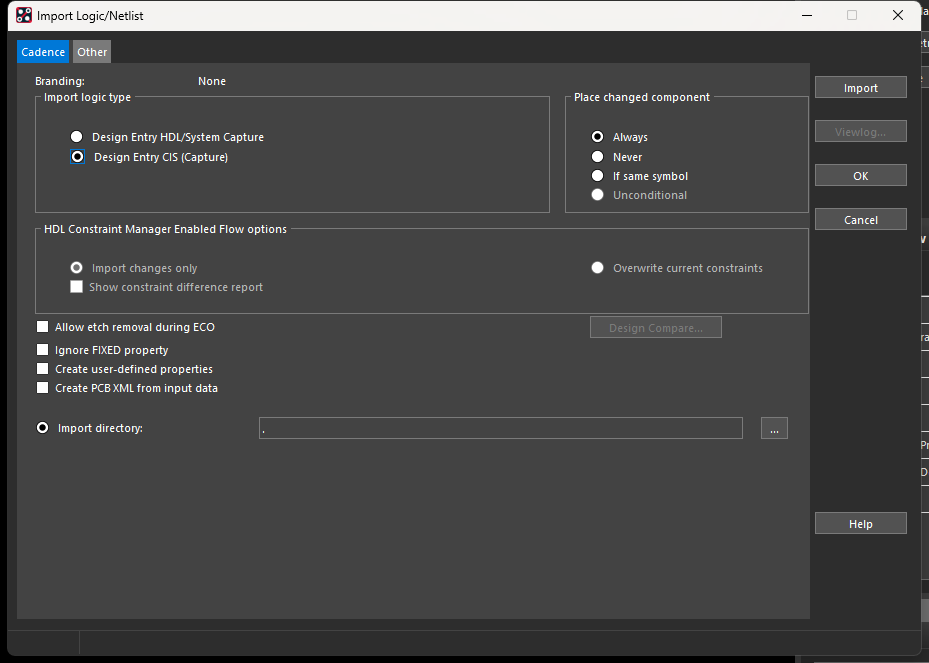

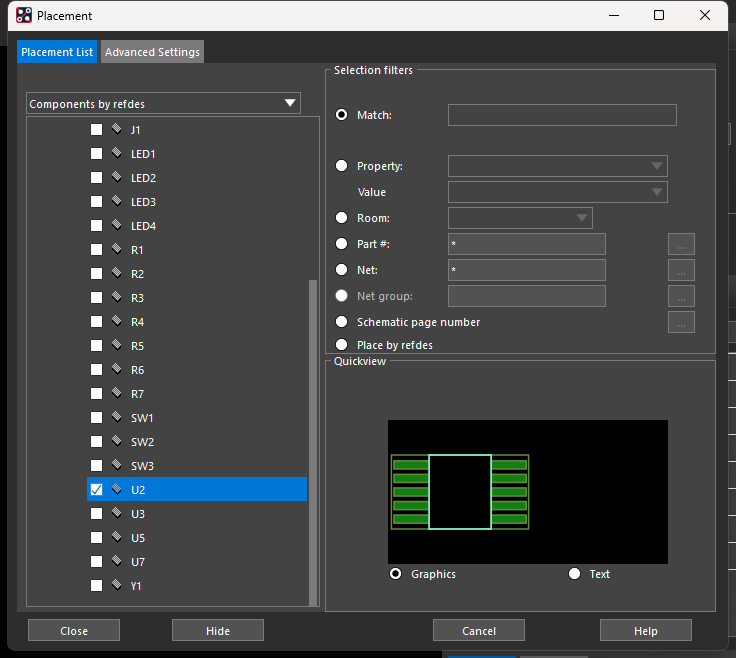

PCB Editor에 import한 Netlist들의 Symbol이 전부 나타나는지 확인한다.

728x90

'Semiconductor > PCB, Virtuoso' 카테고리의 다른 글

| Virtuoso - 기본 Tool 사용법 + Inverter 만들기 (Schemetic ~ LVS) (0) | 2024.08.26 |

|---|---|

| PCB - up_down_controller 설계 4 (PCB 설계) (0) | 2024.04.15 |

| PCB - up_down_controller 설계 2 (FootPrint 설계) (0) | 2024.04.11 |

| PCB 설계 - LED Counter (0) | 2024.04.04 |

| PCB 회로 설계 (0) | 2024.04.01 |