Library Manager 생성

라이브러리 매니저의 Library, Cell, View 생성을 통해 schematic, layout, symbol를 생성하여 사용할 수 있다.

Library 생성

Attach to an existing technology library를 선택해준다.

사용할 gpdk 파일을 선택해준다.

실습은 gpdk090 파일을 사용한다.

gpdk090으로 설정할 경우 design rule은 gpdk090의 기준으로 적용된다.

위 방식을 통해 Library를 생성할 수 있다. 이 Library안에 Symbol, Schematic, Layout을 생성하여 저장할 수 있다.

Schematic 생성

Cell View를 통해 여러가지 Type을 선택하여 생성할 수 있다.

그 중 Schematic을 선택하여 Schematic을 선택하여 생성할 수 있다.

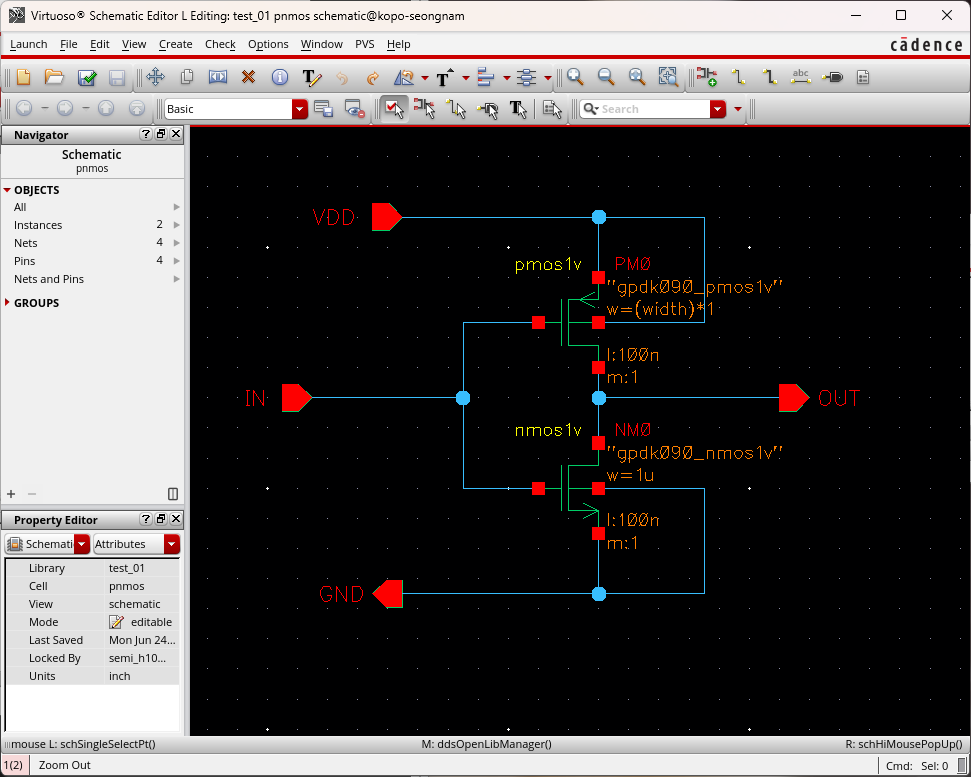

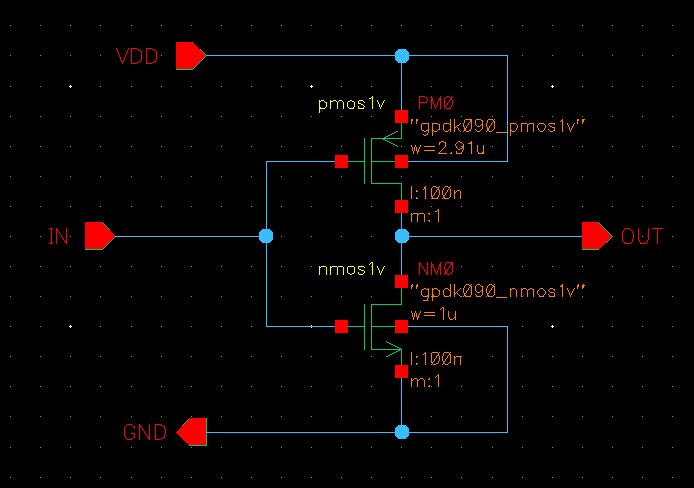

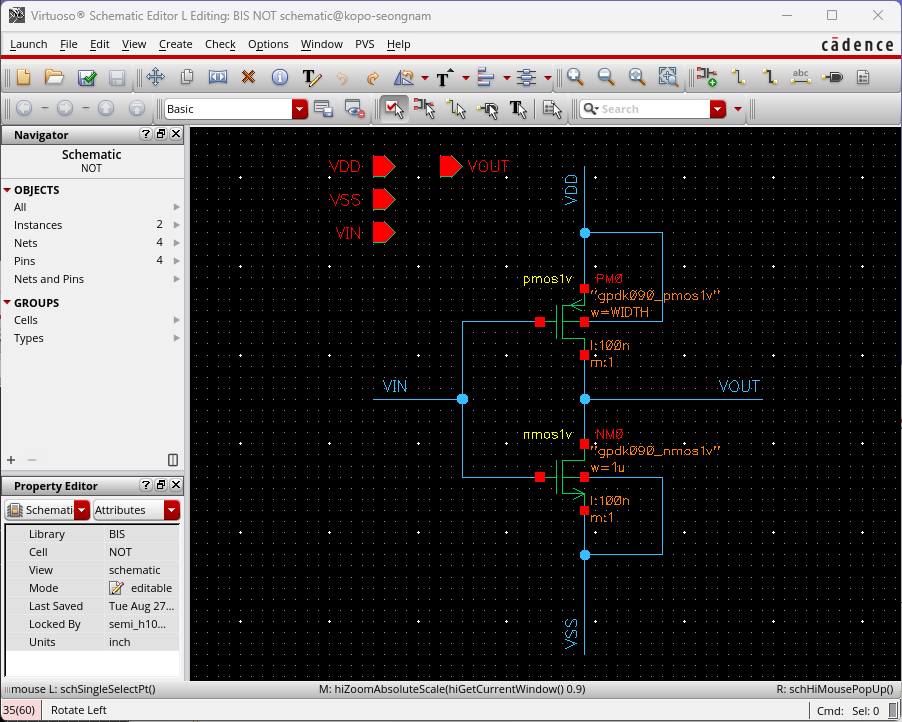

Inverter Schematic 만들기

위와 같이 Inverter에 대한 Schmetic을 그릴 것이다.

* TIP

AND

NMOS : 직렬로 연결한다.

PMOS : 병렬로 연결한다.

OR

NMOS : 병렬로 연결한다.

PMOS : 직렬로 연결한다.

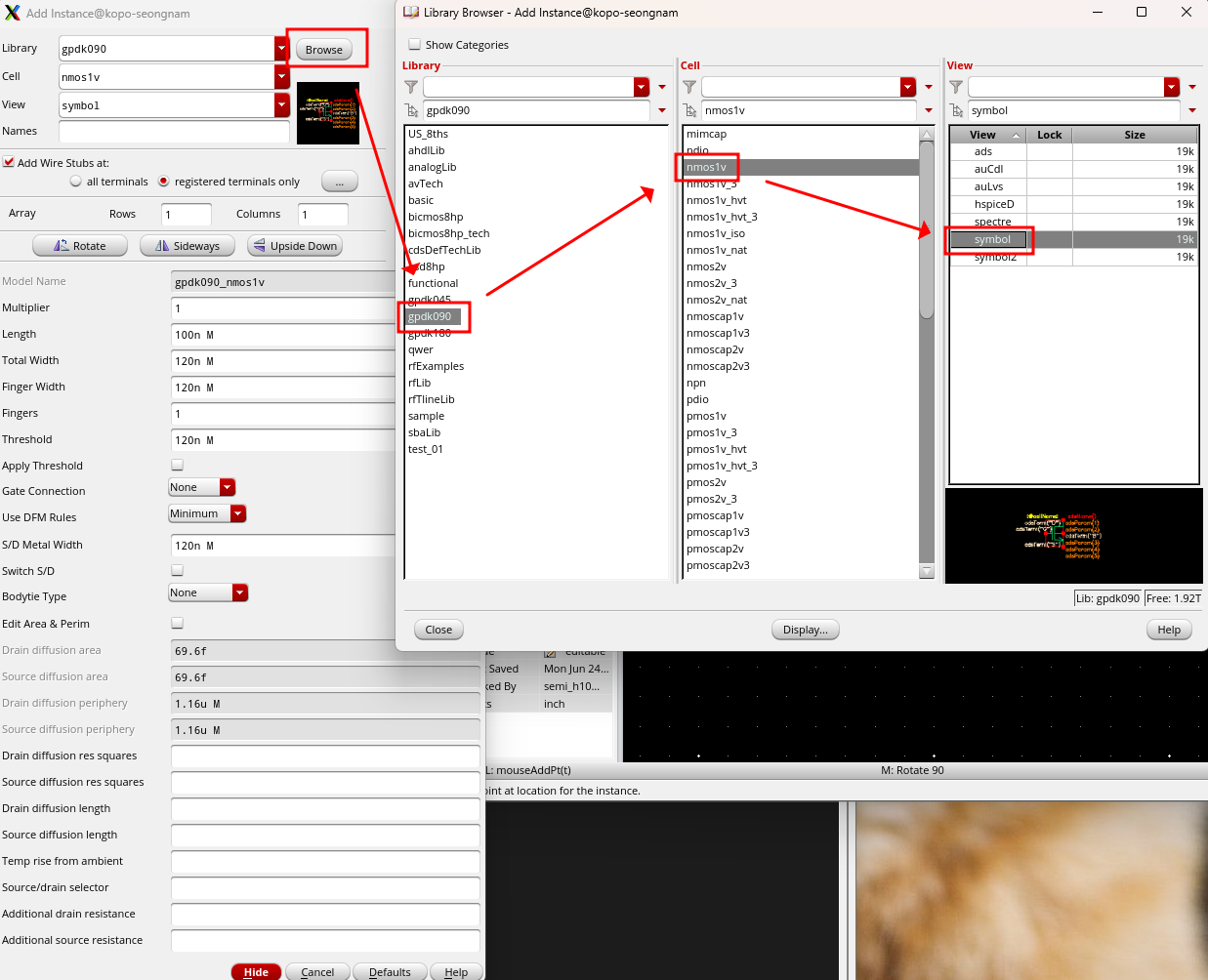

단축키 I를 누르게 되면 Instance를 불러올 수 있고, Library를 통해 원하는 Library의 Cell을 가져다가 사용할 수 있다.

Inverter에는 기본적으로 PMOS와 NMOS를 사용하여 생성한다.

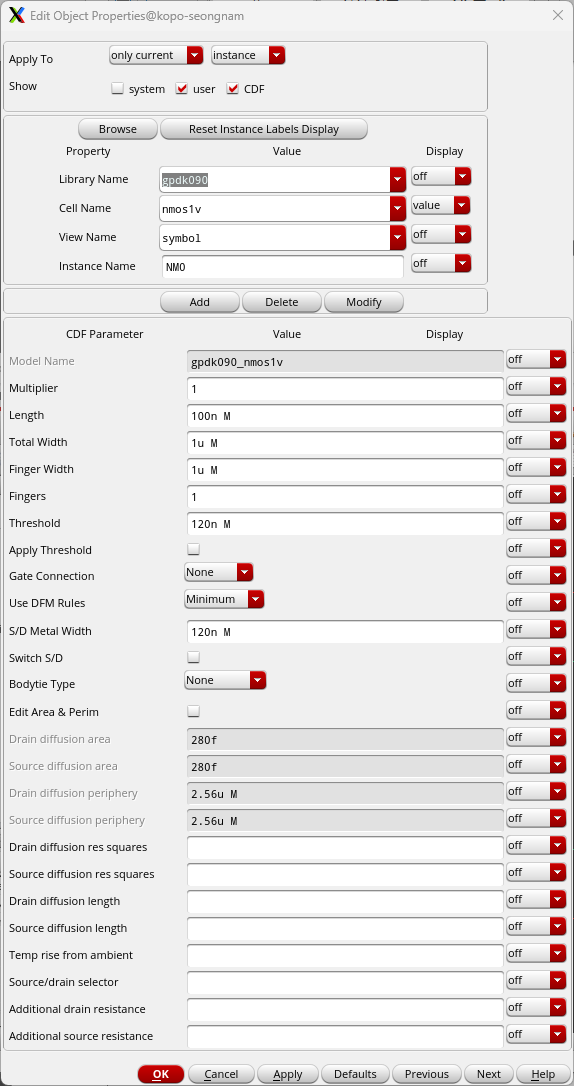

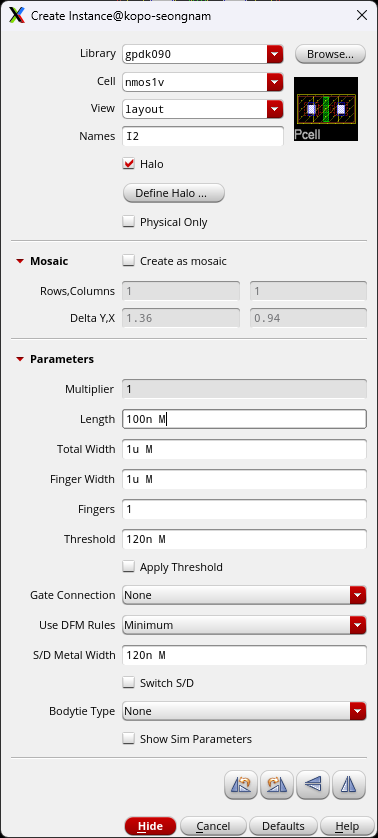

NMOS의 경우 Length는 100n Width는 1u로 설정한다.

* !!!!!!!

100n, 1u로 설정하는 이유는

100n의 경우 해당 기술 노드에서 가장 작은 채널 길이로 설정되어 있는 경우가 많다.

1u의 경우에도 마찬가지로 일반적으로 표준 로직 회로에서 충분한 전류 구동 능력을 제공하면서도, 면적을 지나치게 차지하지 않도록 균형을 맞춘 값이기 때문이다.

추가로 공정사에게 정해주는 기준이 현재 없기 때문에 위와 같은 이유로 최적의 임의의 값을 설정해놓는 것이다.

또한 NMOS를 작게, PMOS를 상대적으로 크게 설계함으로써 필요한 전류를 구동하면서도 칩 면적을 최적화할 수 있다.

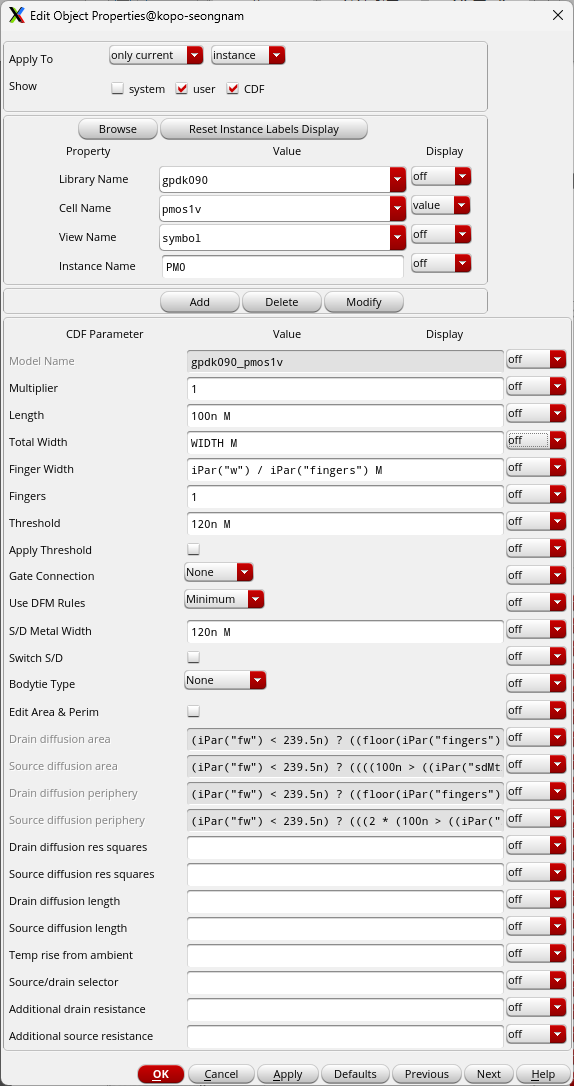

그렇기 때문에 NMOS의 값을 고정시켜놓고 PMOS의 값을 변수로 지정하여 최적의 값을 찾는 것이다.

PMOS는 Length는 임의의 변수로 생성한다. 최적의 Length 값을 찾기 위함이다.

이유는 성능의 최적화를 위해 Simulation을 돌려 최적의 값을 찾기 위함이다. (추후에 값을 찾아서 최적의 값으로 변경할 것이다.)

(현재 위의 PMOS의 WIDTH값은 변수로 지정되어야 하지만 아래에서 수행할 Simulation 값에서 찾은 최적의 값을 넣어놓은 것이다. 원래는 변수로 지정되어 있어야 한다.)

위와 같이 PMOS, NMOS 소자를 배치해준 다음 Interver 구조에 맞게 선 연결 및 Input, Output, VDD, GND 핀을 설정해준다.

소자는 키보드 (i)를 클릭해서 소자를 불러오고 (w)를 이용해서 선을 연결한 다음 (p)를 이용해서 핀을 생성해준다.

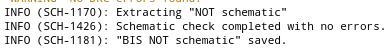

위와 같이 이상이 없음을 확인해야 한다.

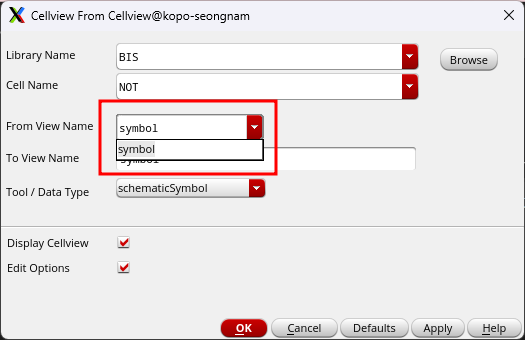

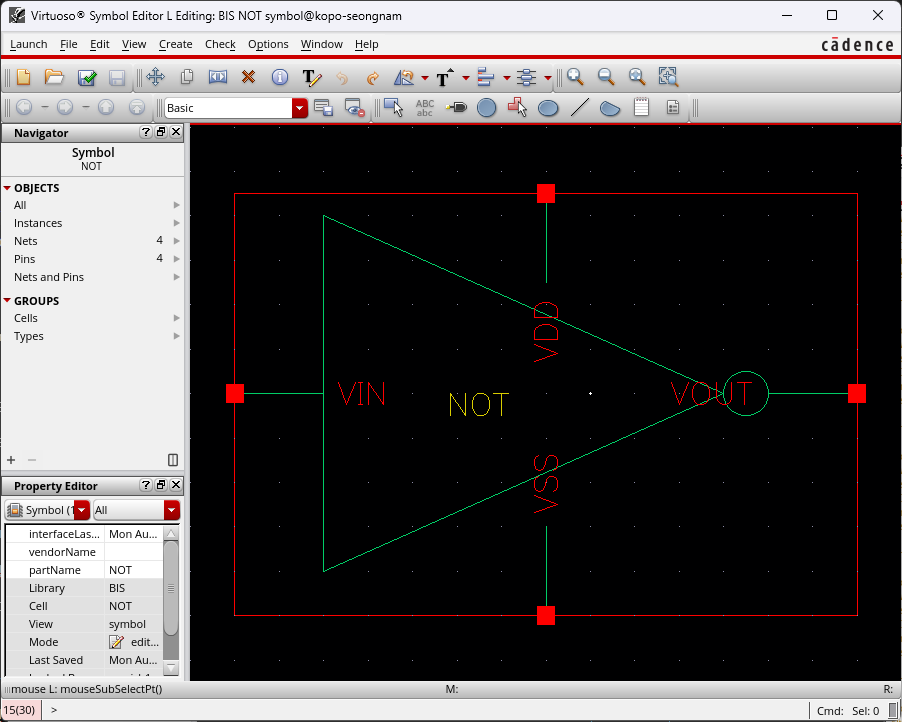

Symbol 생성

기존에 만든 Schematic을 기반으로 Symbol을 생성할 수 있다.

기존의 위와 같은 Symbol을 아래와 같이 실제 해당 게이트의 Symbol처럼 모양을 변경할 수 있다.

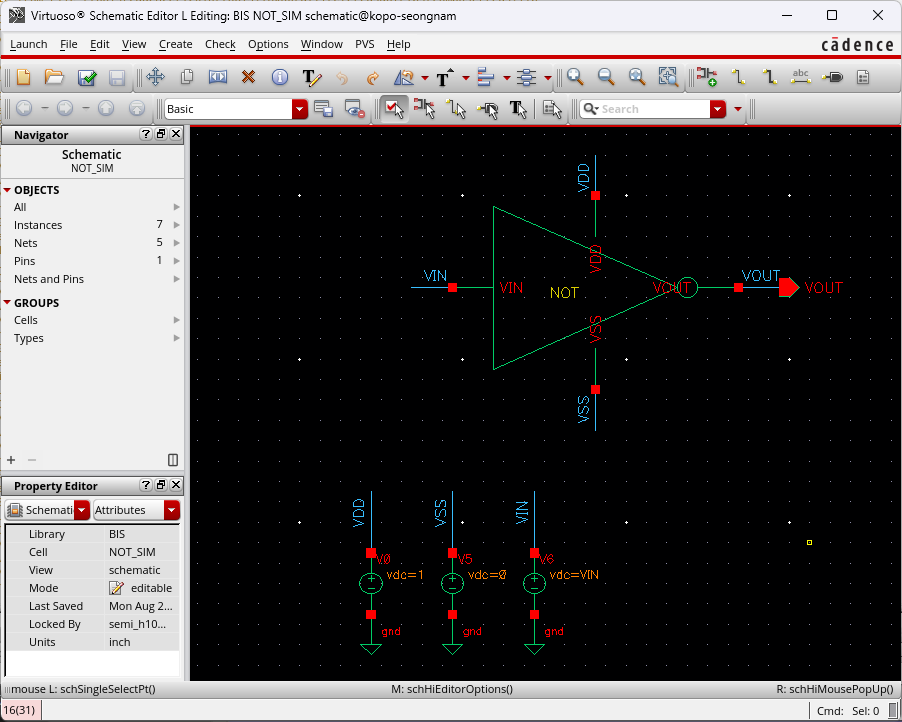

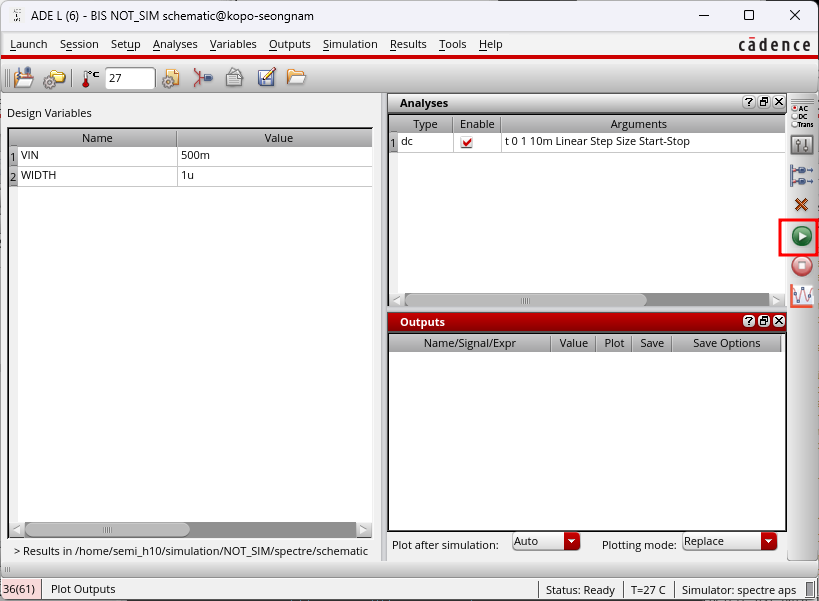

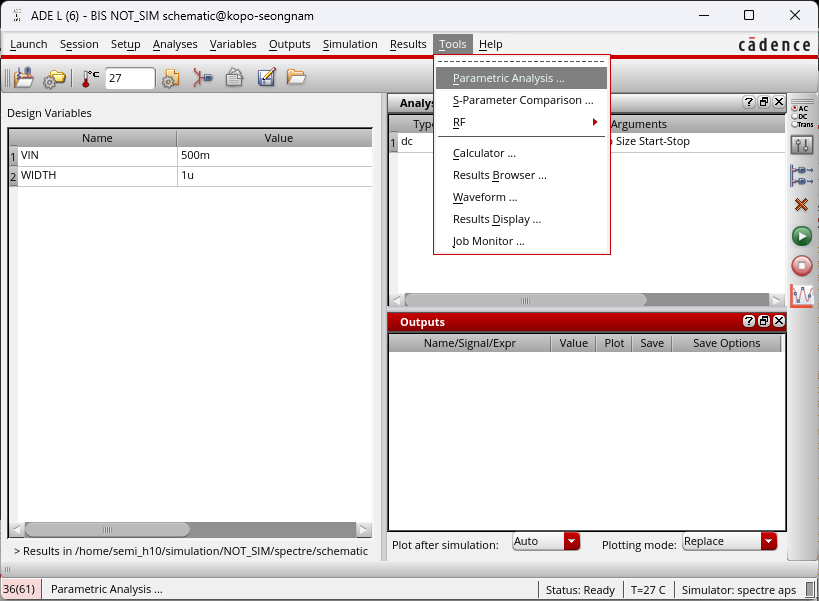

Simulation 생성 및 수행

기존읜 Schematic은 위와 같고 width의 경우 변수로 지정되어 있다.

Simulation을 수행하기 위한 Schematic을 새롭게 생성한다.

Simulation용 Schematic을 위와 같이 생성한다.

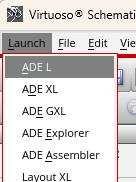

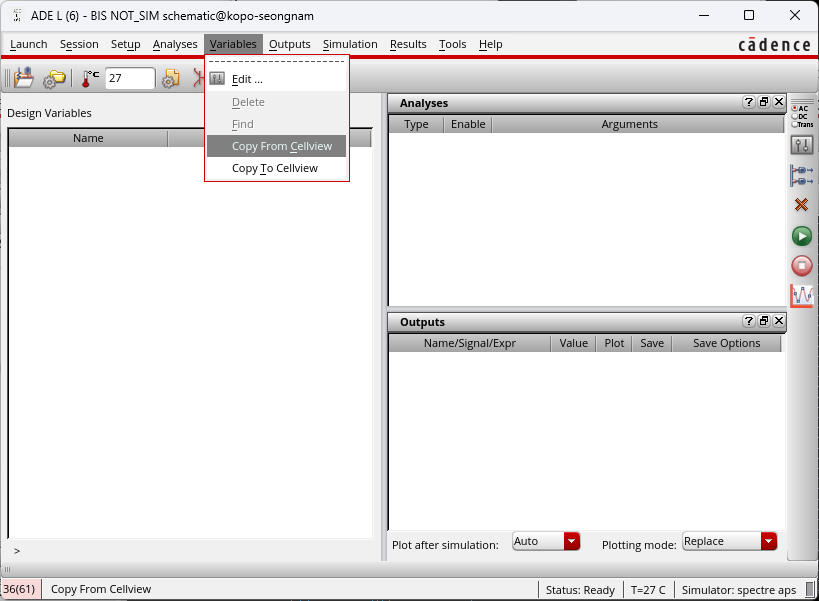

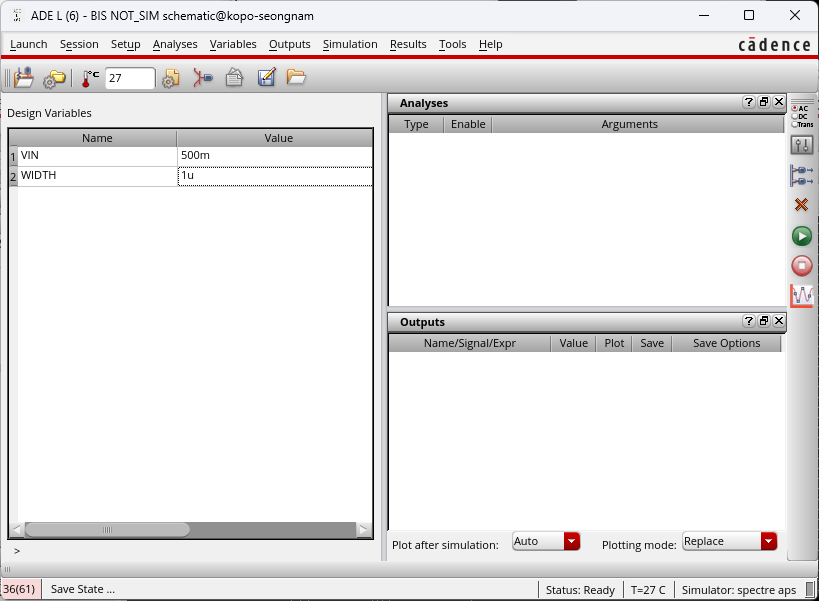

Cell View에서 정의된 변수들을 ADE L 환경으로 복사하는 기능이다.

변수의 Value는 임의로 넣는다 Simulation을 통해 수치가 변경되기 때문에 넣는 값은 크게 의미가 없다.

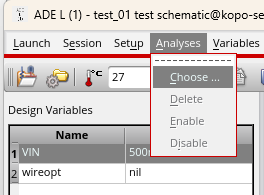

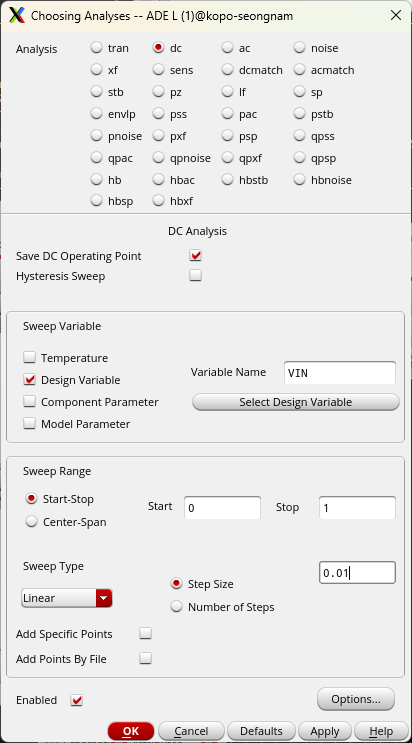

Simulation을 돌리기 분석 정보에 대한 설정을 해준다.

VIN에 대한 정보를 입력한다.

VIN에 DC, 0~1까지 0.01 간격을 두고 전압을 전달할 것이다.

linear를 통해 선형적으로 값을 표현한다는 의미를 가진다.

Netlist and Run 버튼을 느르게 되면 설정된 Simulation이 실행된다.

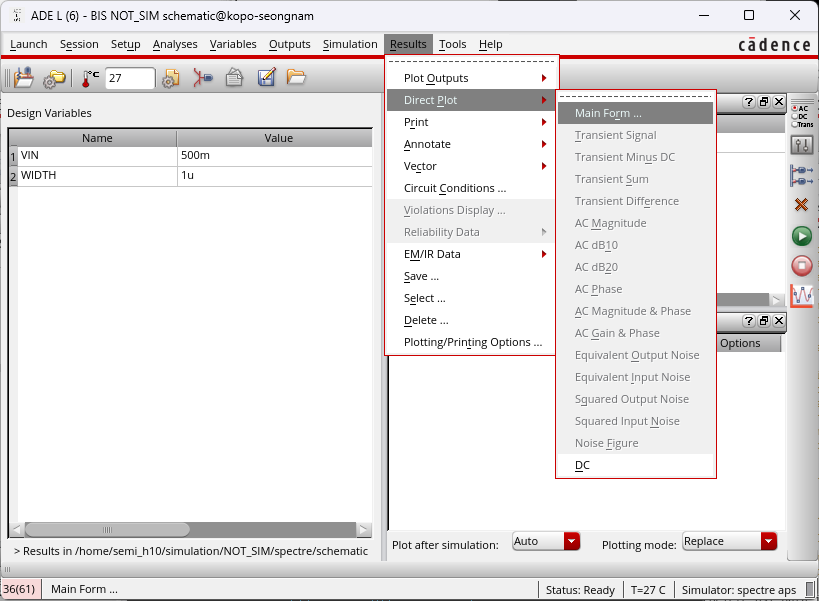

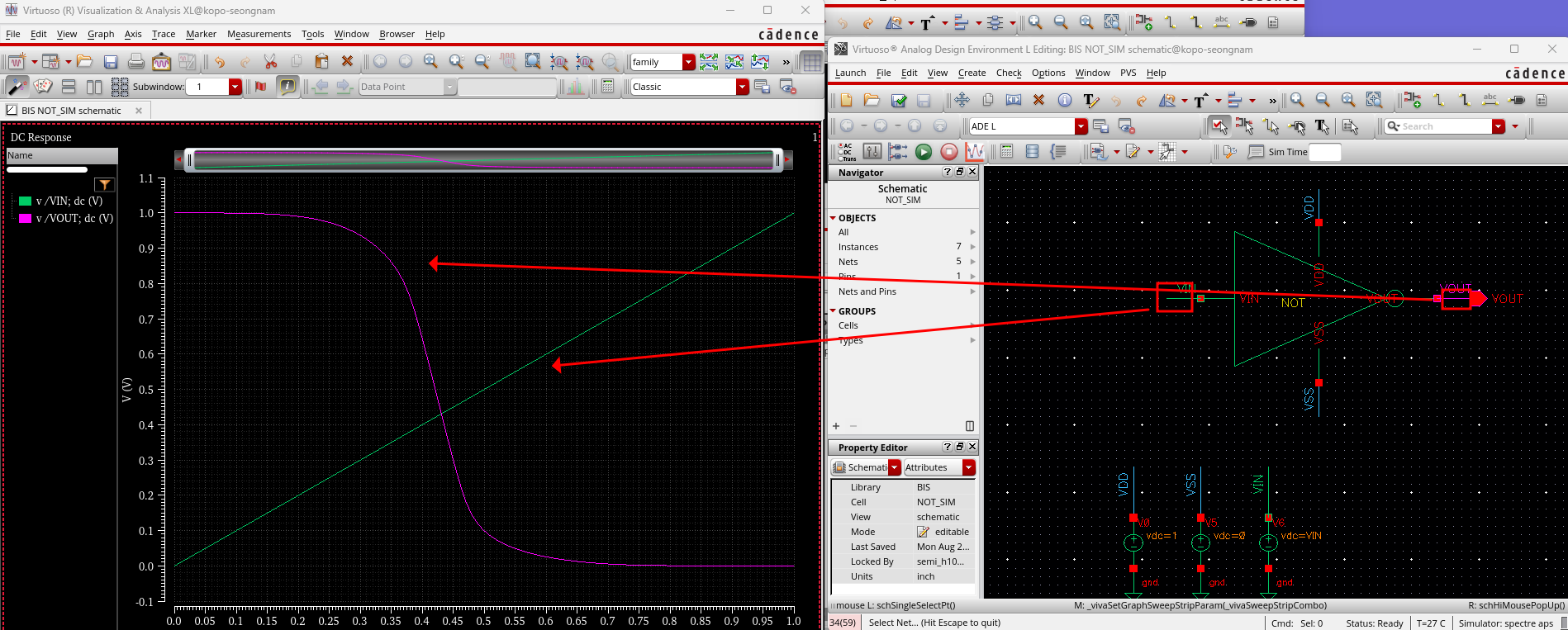

Main Form을 통해 신호를 linear로 확인 가능하며 Schematic에서 자신이 보고 싶은 신호를 클릭해준다.

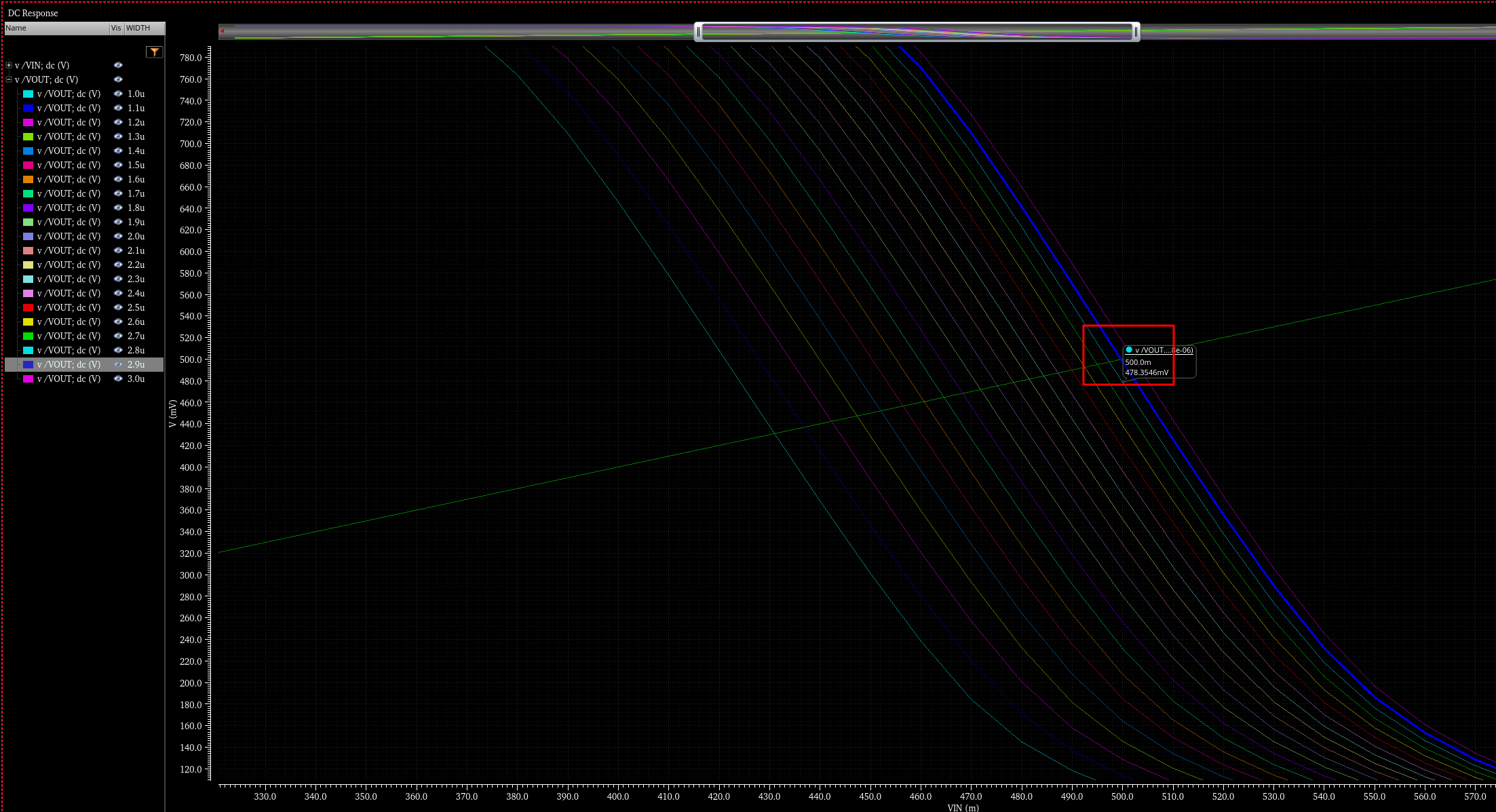

위 값은 임의로 지정한 VIN 0.5V WIDTH 1u일 때 값이다.

Simulation 결과는 VIN이 0.5V일 때 출력이 0.5V가 나와야 하는데 그렇지 않기 때문에 WIDTH를 수정해야 한다.

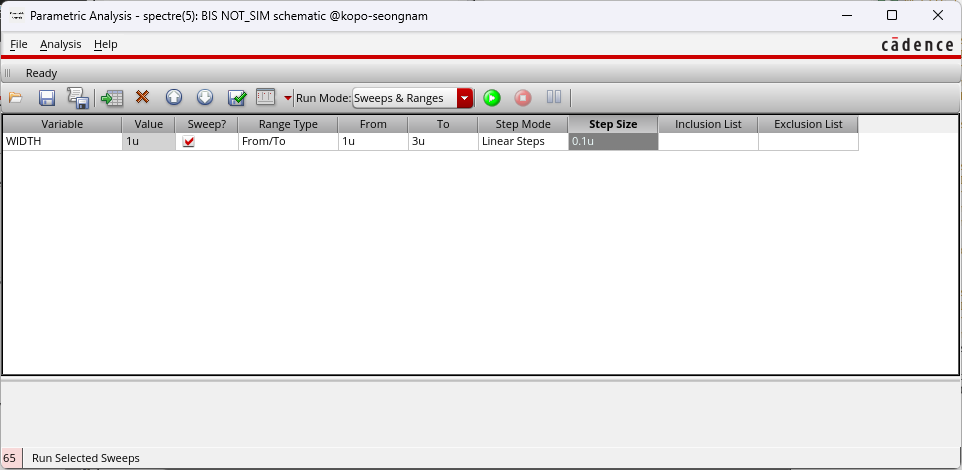

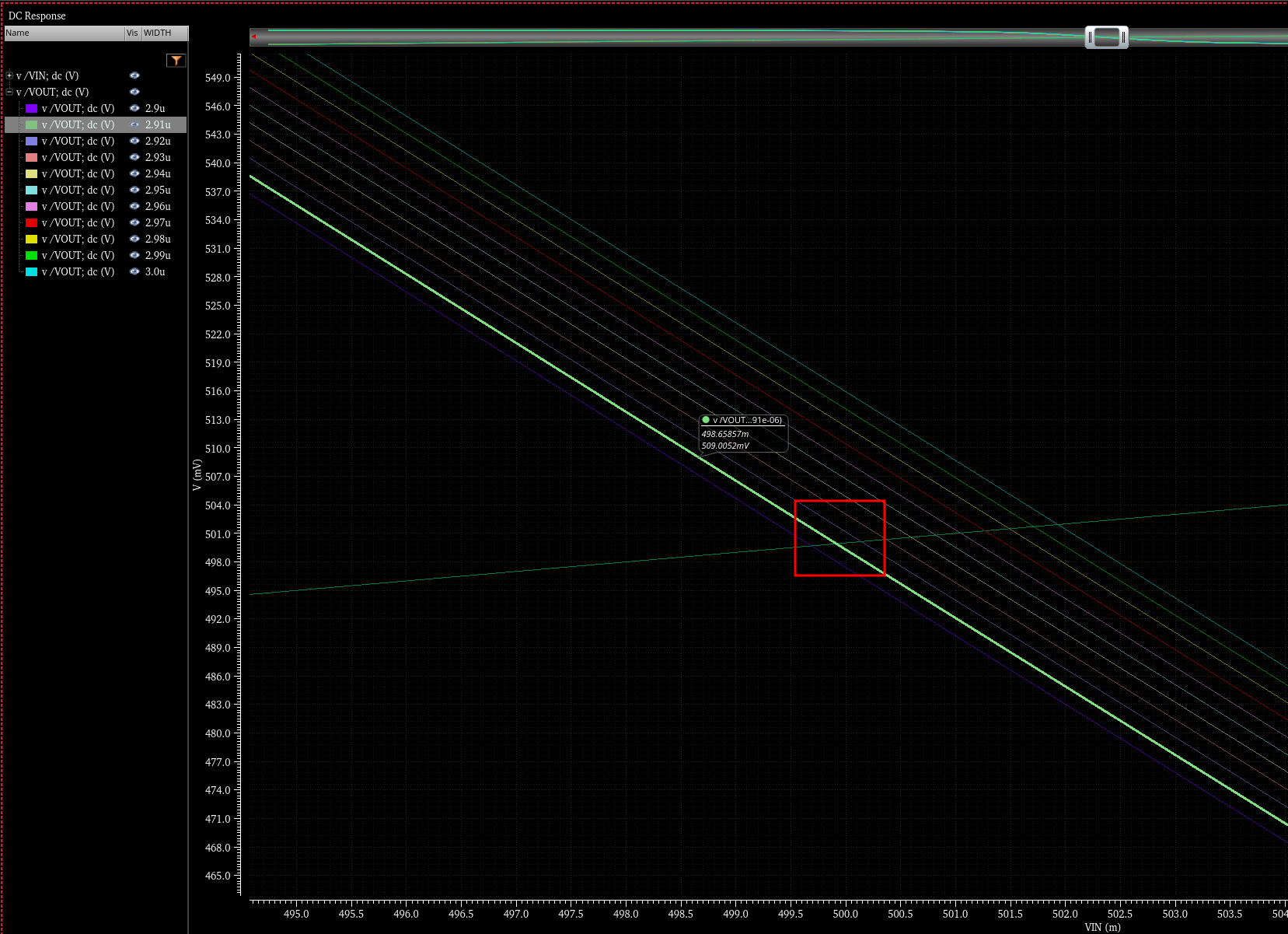

WIDTH의 값을 1u~3u까지 0.1의 간격으로 임의의 범위를 지정해서 1차 확인을 한다.

선이 작아서 잘 안보이겠지만 500에 해당하는 값이 2.9u와 3.0u 사이에 있는 것을 볼 수 있다.

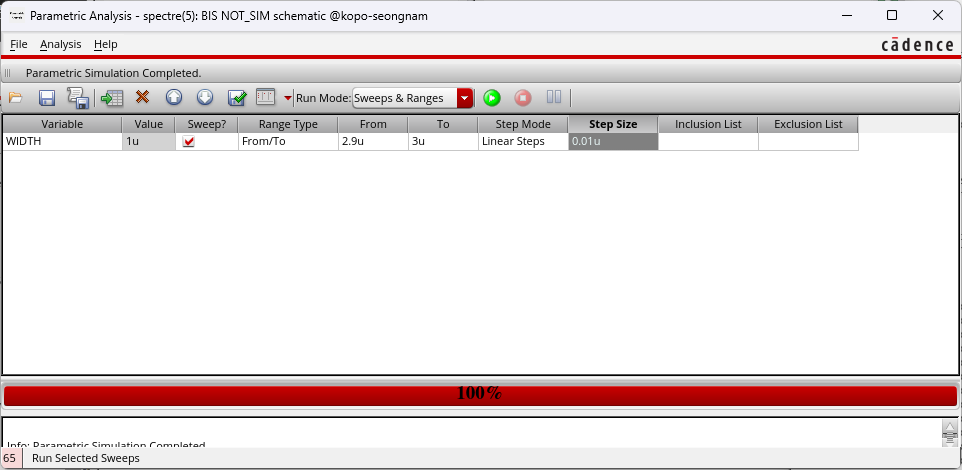

더 자세하게 값을 찾기 위해 2.9u ~ 3.0u까지 0.01u 간격으로 찾아본다.

0.01 간격으로 Simulation을 돌려보았을 때 2.91u~2.92 사이의 값이 가장 최적의 값인 것을 볼 수 있다.

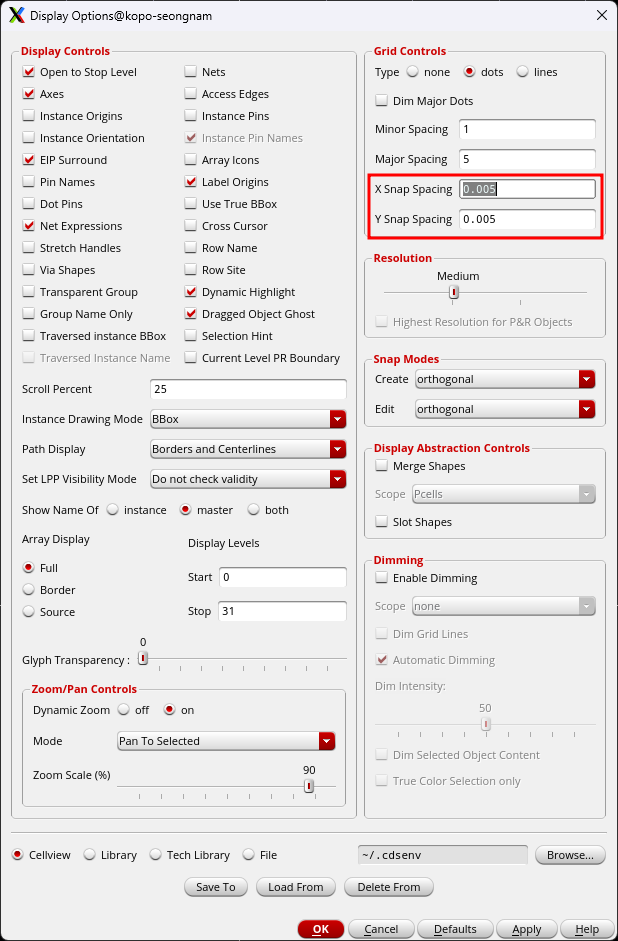

Smultaion의 효율성과 해상도에 의해 0.005 단위의 값으로 최적의 값을 찾는 것이 좋기 때문에 2.91u~2.92u 사이의 값 중 0.005u 간격으로 최적의 값을 정한다.

여기서는 2.91u가 최적의 값이라고 지정한다.

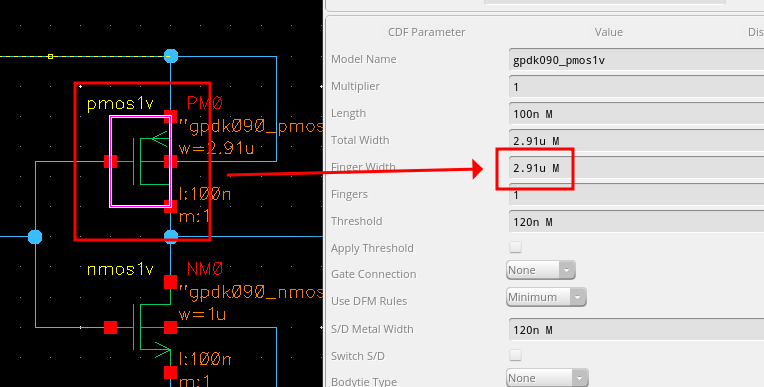

PMOS의 Width를 2.91u로 변경한다.

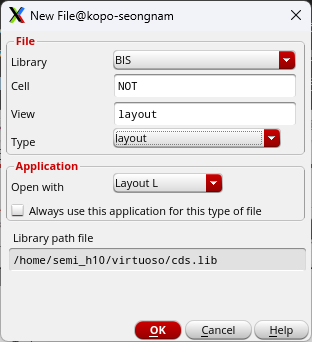

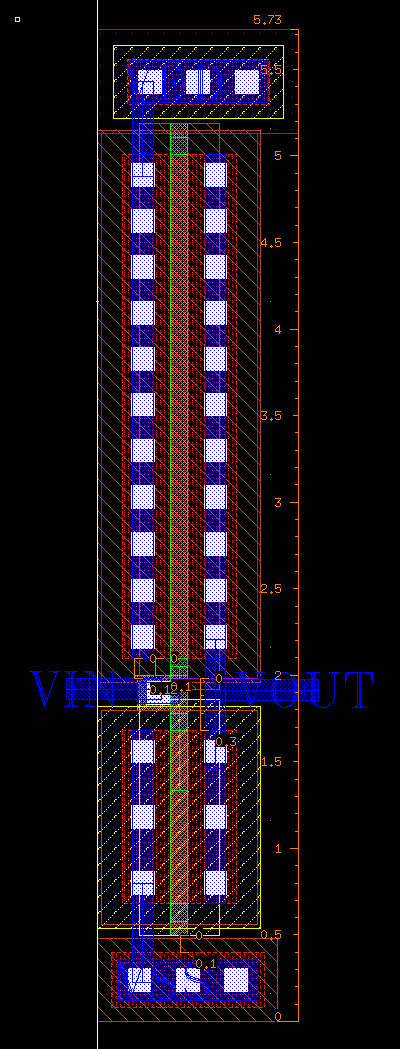

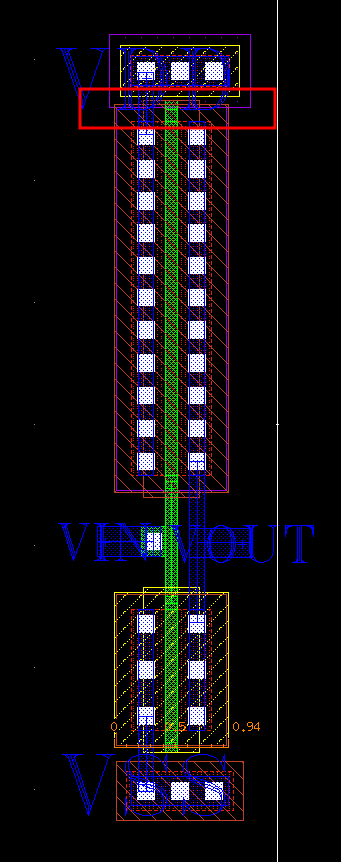

Layout

Smulation을 통해 최적의 값을 찾았기 때문에 해당 값을 가지고 Layout을 그려준다.

Layout은 기본적으로 위에서 말했지만 gpdk090의 Design Rule을 따른다. (추가적으로 해당 Rule은 gpdk090_referenceManual을 통해 확인이 가능하다.)

단축키 O와 I를 통해 필요한 소자들을 불러와 Layout을 진행해준다.

완성하게 되면 위와 같은 Layout을 확인할 수 있다.

Layout을 그리는 순서 (정석은 아니고 일반적인 진행단계)

1. I 단축키를 이용하여 gpdk090에 있는 PMOS, NMOS를 지정된 크기로 설정하여 배치한다.

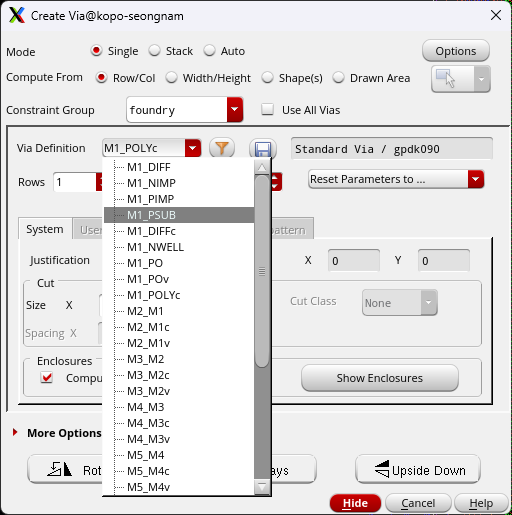

2. O 단축키를 이용하여 Via를 설정해준다. (Via는 이후 VDD와 VSS를 연결하는 역할을 한다.)

3. 이후 Design Rule에 맞게 소자들을 최소한의 크기로 배치한다.

(ex) Poly와 Oxide의 간격은 최소 0.1u 이상 / Metal 간격은 0.12u 이상 등...)

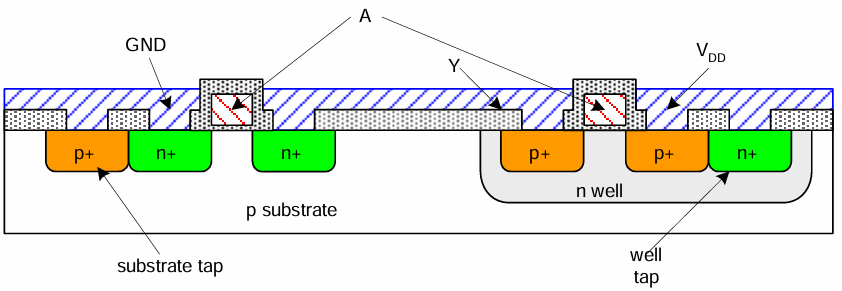

+ 기본적으로 Layout의 기본은 P-Sub이다. 그렇기 때문에 N-Well을 통해 PMOS와 VDD를 연결할 Via는 서로의 N-Well을 공유해주거나 별도의 N-Well을 지정하여 하나로 묶어준다.

위 그림처럼 N-Well은 별도로 생성해주기 때문에 서로 겹치게 만들어주지 않거나 하나로 묶어주지 않으면 N-Well이 끊기기 때문이다.

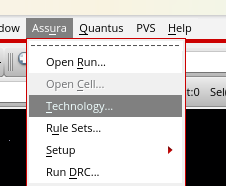

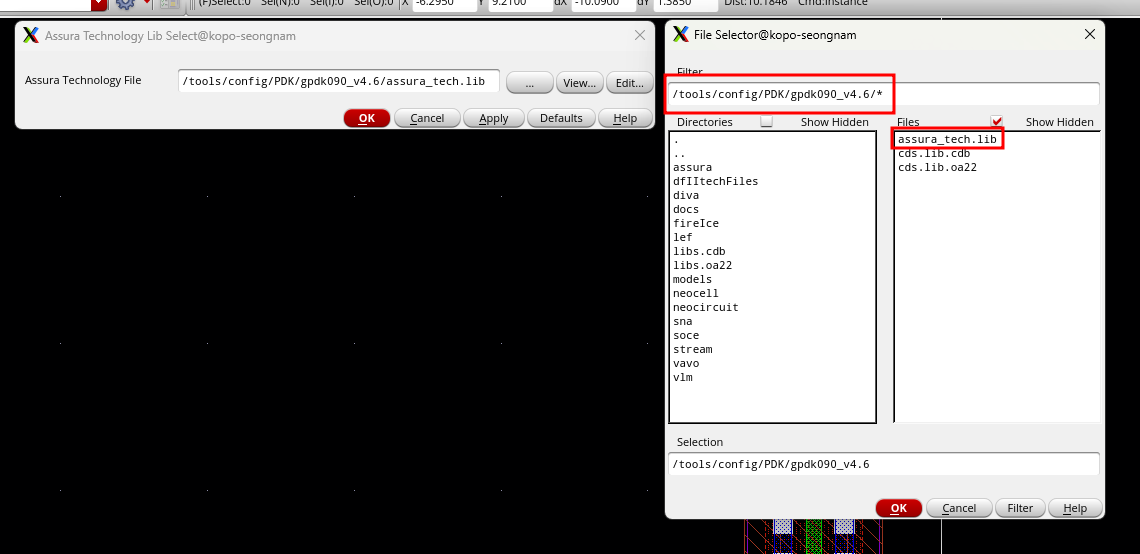

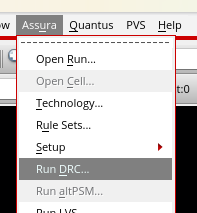

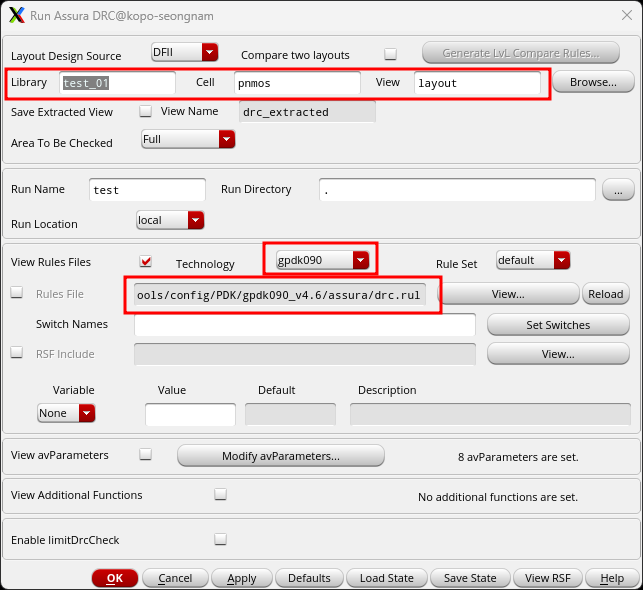

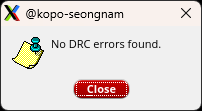

DRC

Design Rule Check

DRC Check를 위해서는 Tech 파일로 gpdk090에 관련된 Asura 파일(검증)이 필요하다.

해당 파일을 추가해준다.

에러가 발생하면 해당 에러를 확인하고 해결해준다.

만약 에러가 없다면 아래와 같이 DRC errors가 없다는 문구가 나온다.

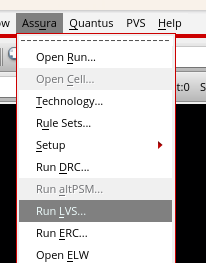

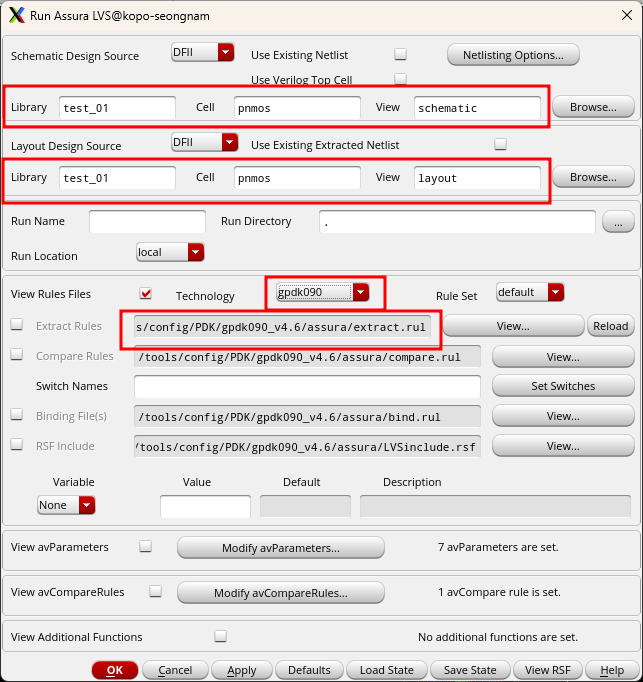

LVS

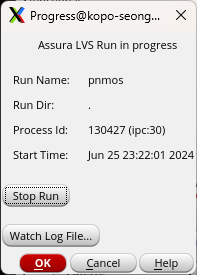

Layout Versus Schematic의 약자로 레이아웃이 설계된 회로의 Schematic과 일치하는지 확인하는 과정이다.

비교하는 Schematic과 Layout 경로를 잘 맞춰줘야 한다.

마찬가지로 LVS를 진행해주고 이상이 없으면 위와 같이 Successful이라는 문구를 확인할 수 있다.

LVS 에러 발생 시

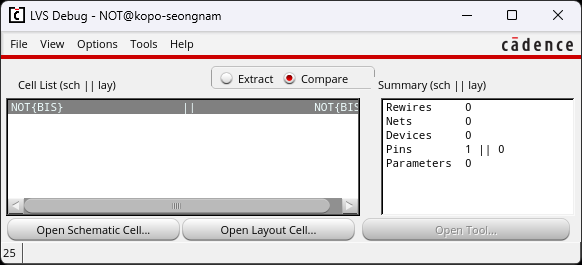

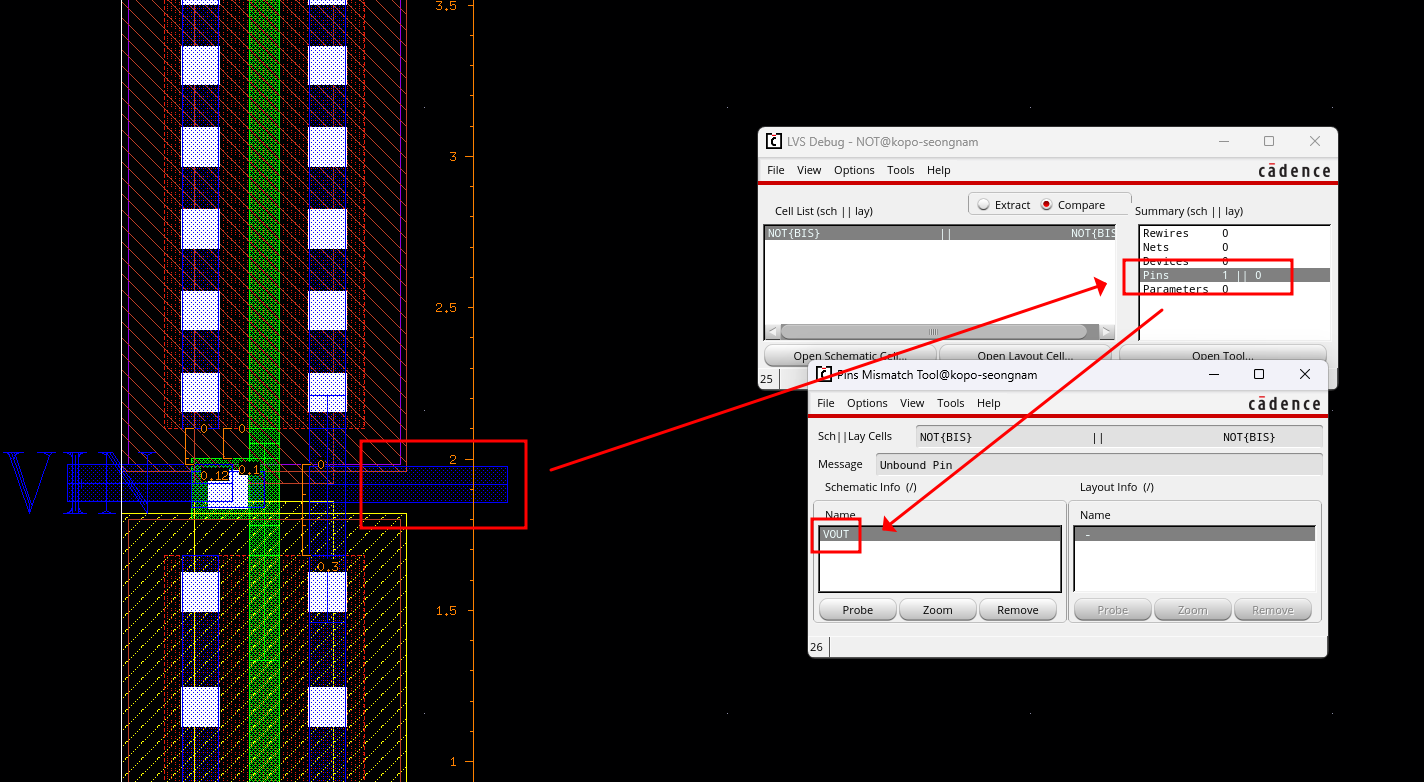

위와 같이 LVS Debug 화면이 뜨게 된다.

우측의 Summary 부분의 아래 Parameters부터 클릭해가면서 해결해 나가면 된다.

위와 같이 VOUT을 일부러 없애면 위와 같이 에러에 VOUT이 없어서 뜬 에러라고 나타난다.

+ Metal의 길이는 어차피 추후에 One Chip에 연결되는 부분이기 때문에 최소 길이나 넘으면 길게해도 상관없다.

Error!!!!!

DRC Check에서 에러가 발생했는데 위의 VDD 소자를 PMOS의 보라색 선이 일치해야 해결되는 문제가 있었다.

[Virtuoso] Lock된 파일 강제로 해제하는 방법

Cadence Virtuoso에서 여러 명이서 협업을 하거나, 혹은 내가 만든 회로를 다른 사람에게 전송할 때, Lock관련 문제가 발생하는 것을 확인할 수 있다. Lock File이 생기면 해당 파일에 대해서는 읽기 전용

made-by-tia.tistory.com

추가로 virtuoso Lock이 걸려 edit이 불가능한 경우 위 블로그를 참고하여 해결하자!

'Semiconductor > PCB, Virtuoso' 카테고리의 다른 글

| Virtuoso - 2x1 MUX(Logic, Switch) / XOR(Logic, Switch) (0) | 2024.08.27 |

|---|---|

| Virtuoso - 2NAND / 2NOR (Schematic ~ Layout) (0) | 2024.08.26 |

| PCB - up_down_controller 설계 4 (PCB 설계) (0) | 2024.04.15 |

| PCB - up_down_controller 설계 3 (FootPrint, Via Pad 설계 / PCB Footprint 확인 및 설정 / Netlist 파일 생성 및 import) (0) | 2024.04.12 |

| PCB - up_down_controller 설계 2 (FootPrint 설계) (0) | 2024.04.11 |