Stick Diagram (2x1 MUX, XOR Switch 회로)

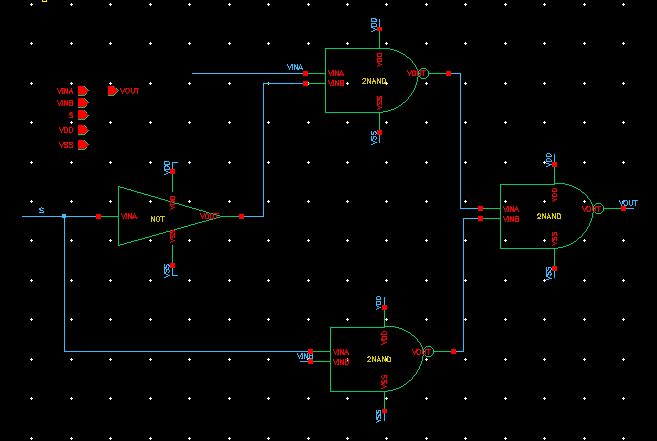

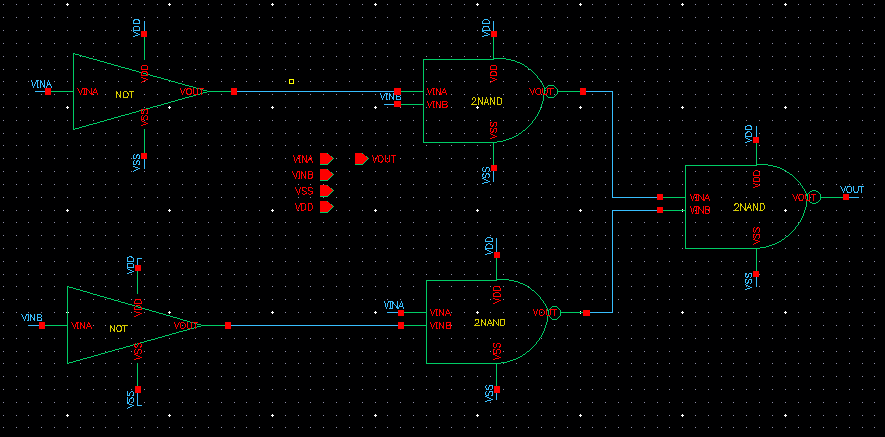

2x1 Mux(Logic)

Mux는 기본적으로 S(Select) 값에 의해 출력값이 정해지는 논리 회로다.

Y = (A * Sbar) + (B * S) 와 같이 논리식을 표현할 수 있다.

하지만 기본적으로 Layout 설계시 NAND, NOT 게이트를 사용하여 구성하는 것이 일반적이다. 그 이유는 가장 적은 수의 트랜지스터를 가지고 논리 게이트를 구성할 수 있기 때문이다.

AND = NAND + NOT

OR = NOT, NOT + NAND

위와 같이 AND, OR 게이트를 NANA와 NOT으로 구성할 수 있다.

위 그림의 위쪽은 Mux를 AND, OR를 NAND, NOT을 통해 구성한 그림이고 NOT + NOT은 원래 처음 들어간 값이 나오기 때문에 결국 Mux의 논리 회로는 아래와 같이 3개의 NAND를 통해 표현할 수 있는 것을 알 수 있다.

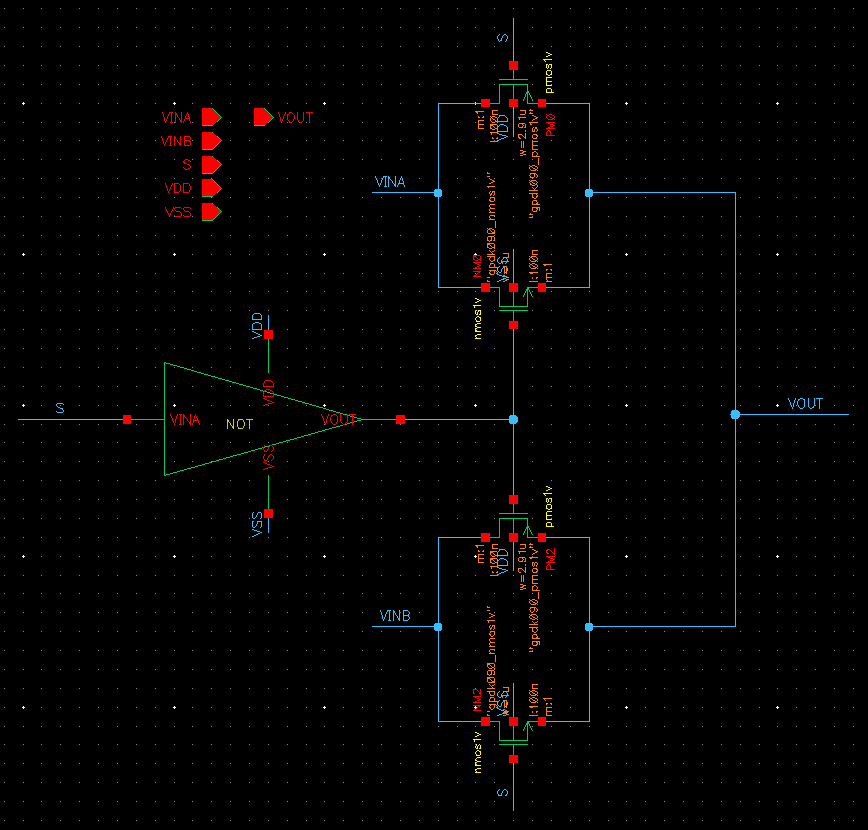

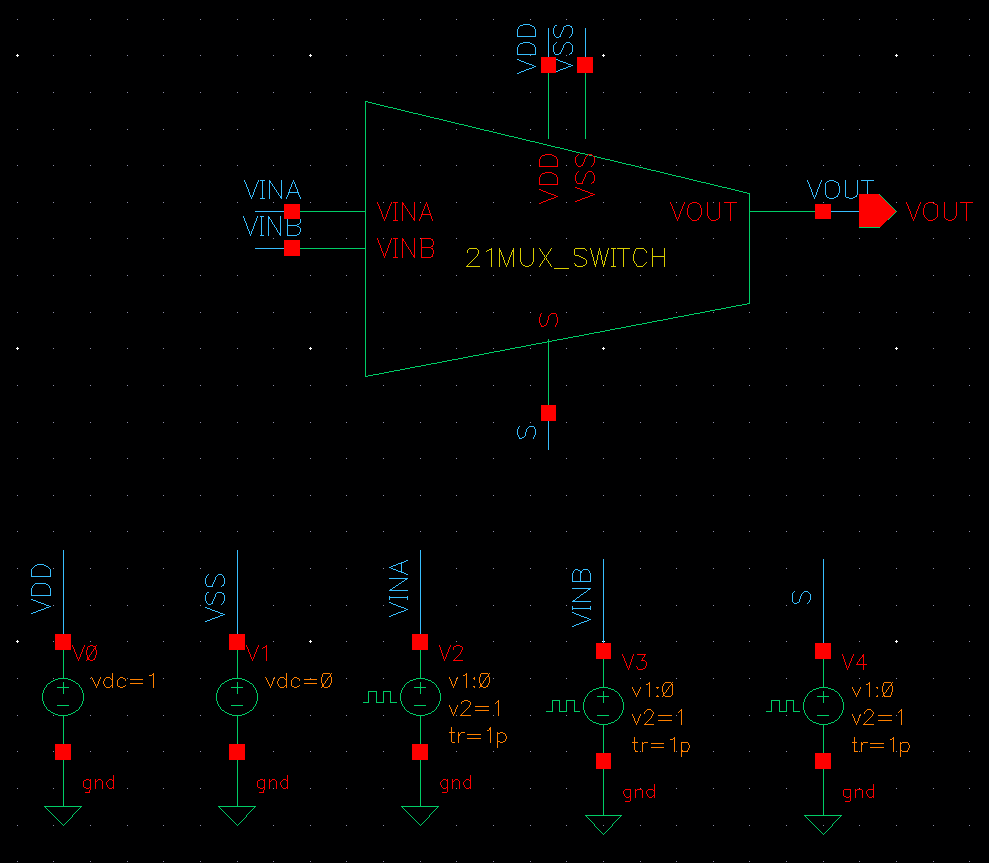

Schematic

Transmission Gate는 S, S_bar를 입력값으로 주기 때문에 아래와 같이 Schematic을 그리게 된다.

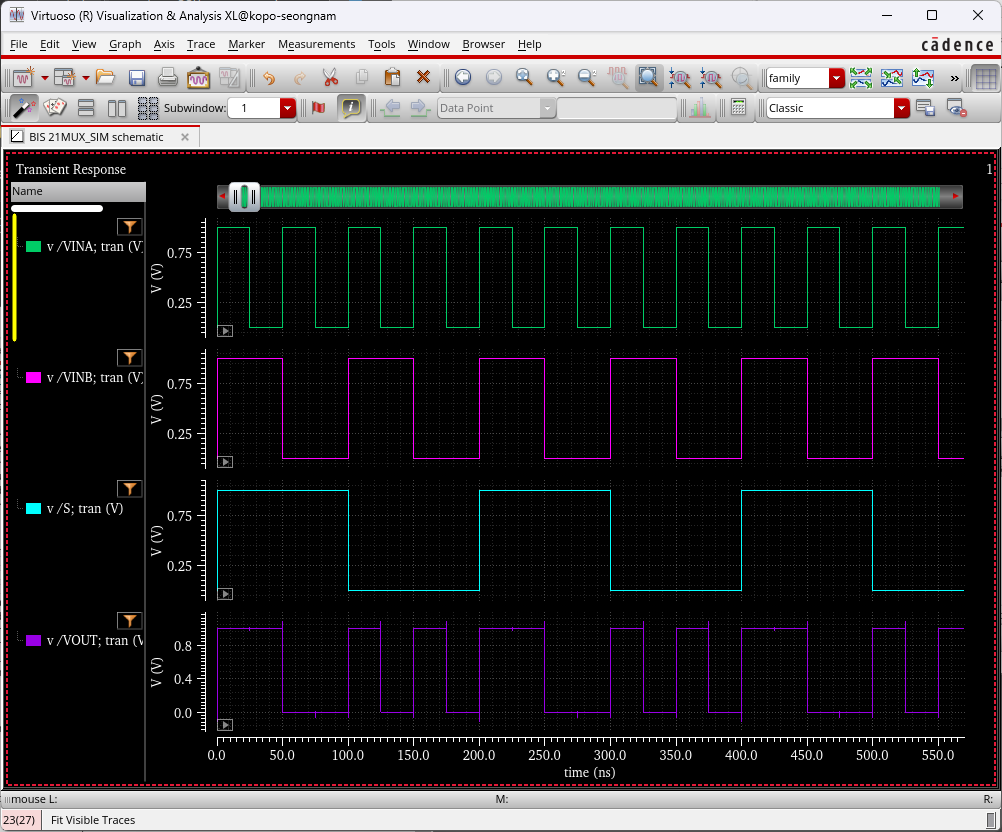

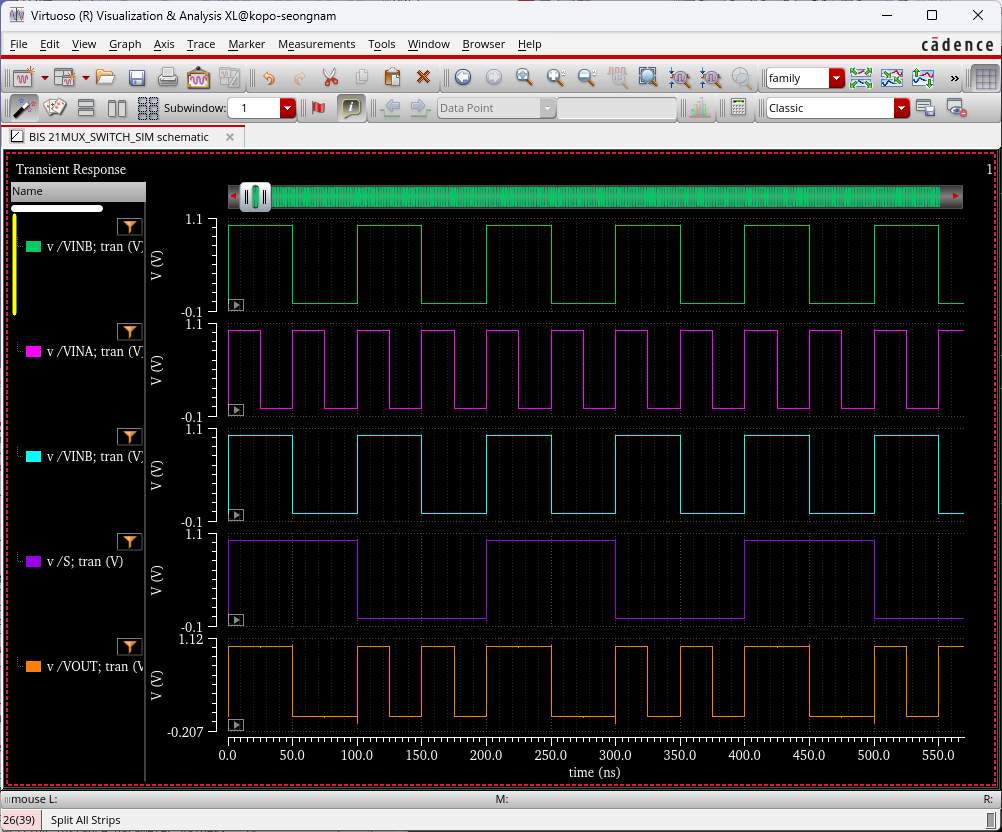

Simulation

vpulse를 통해 변화되는 값을 주입하여 의도한 Mux 값이 나오는지 확인한다.

입력 S의 값이 1이면 VINB의 파형이 입력 S의 값이 0이면 VINA의 파형이 VOUT으로 출력되고 있는 것을 확인할 수 있다.

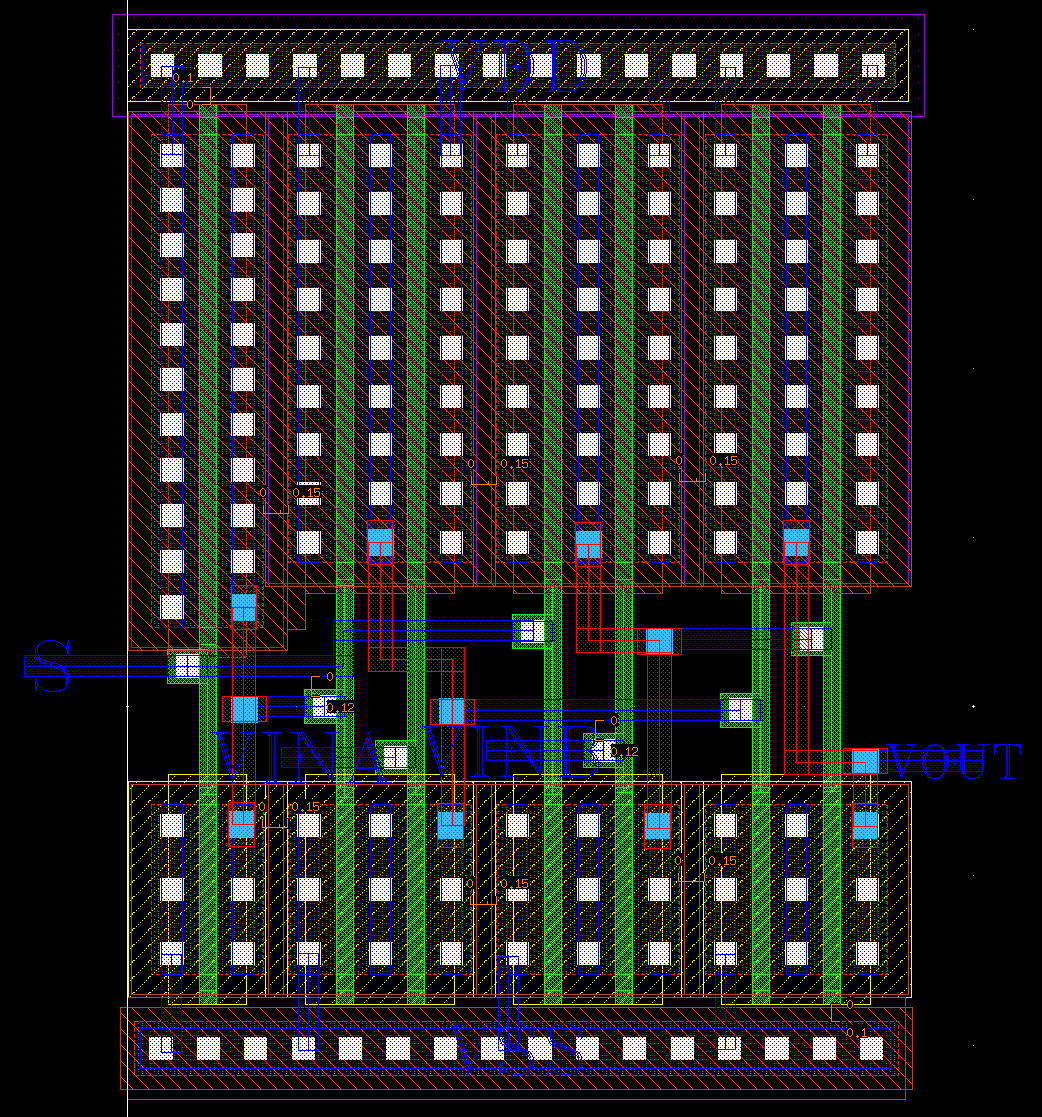

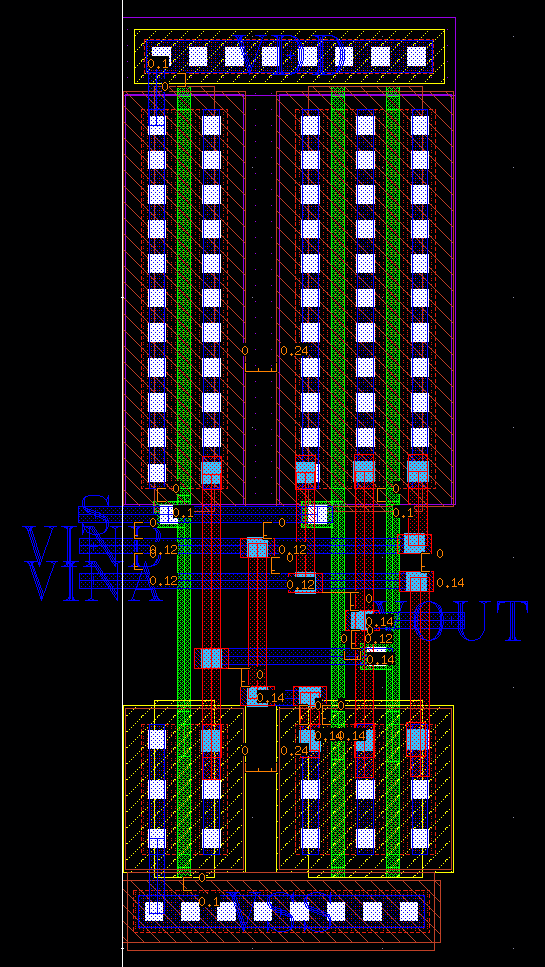

Layout

위에서 그린 Schematic을 참고하여 gpdk090 Design Rule 위배하지 않는 선에서 최소한의 면적으로 Mux Layout을 위와 같이 설계한다.

2x1 Mux(Switch)

Schematic

Simulation

Stick Diagram

Layout

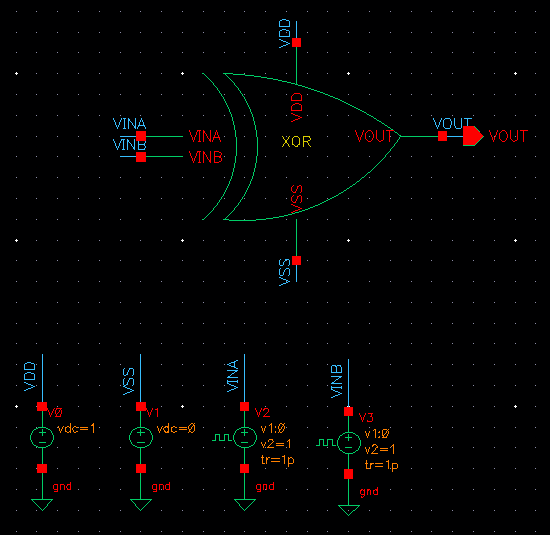

XOR(Logic)

Schematic

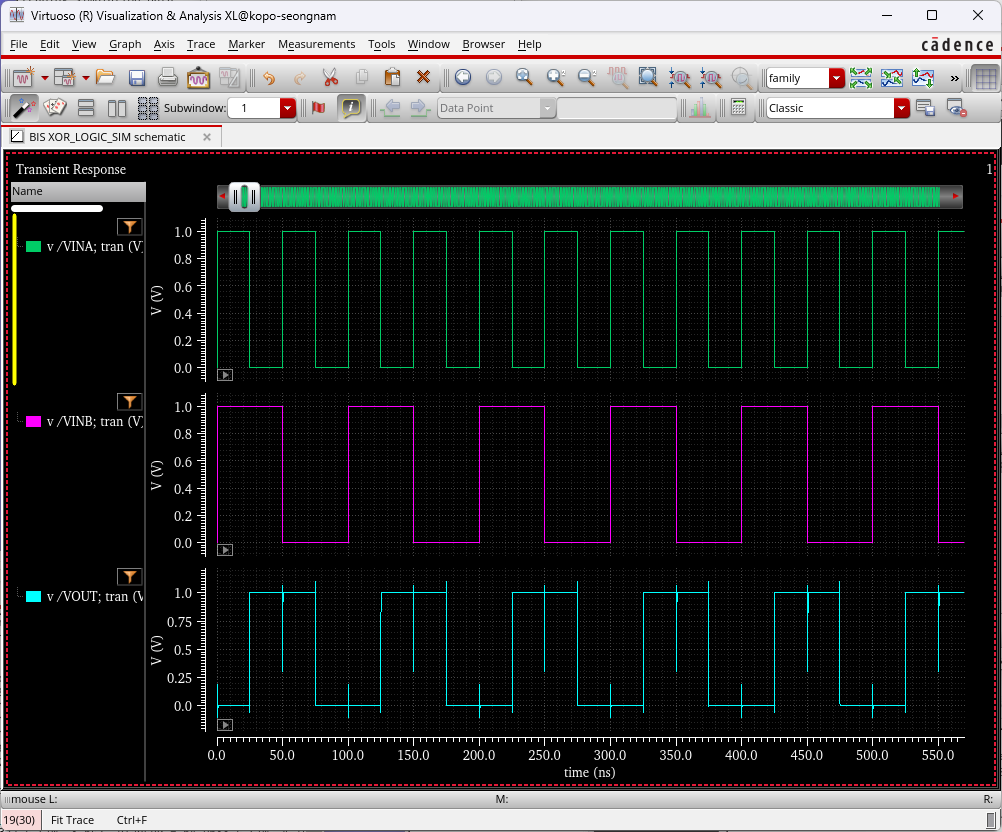

Simulation

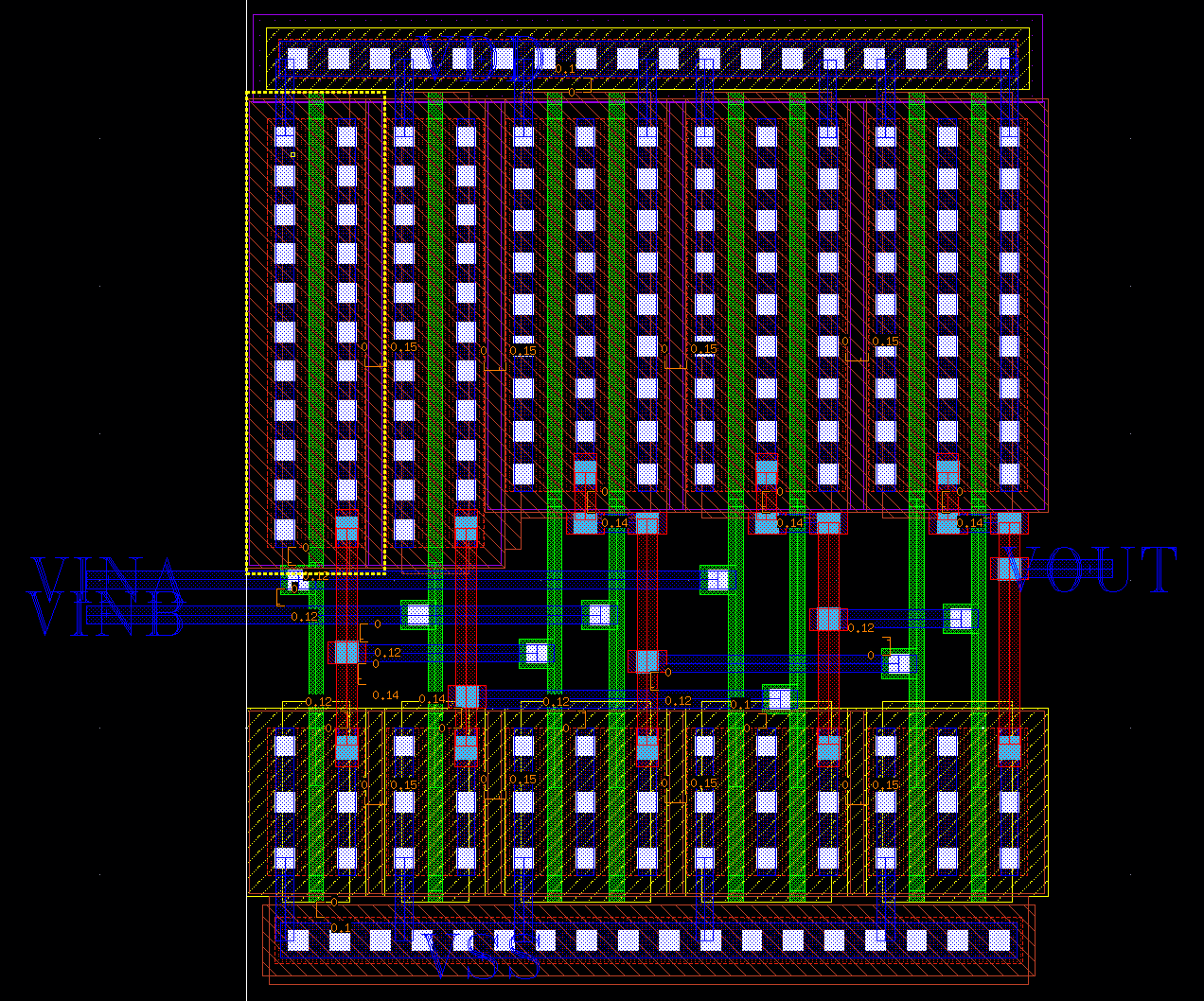

Layout

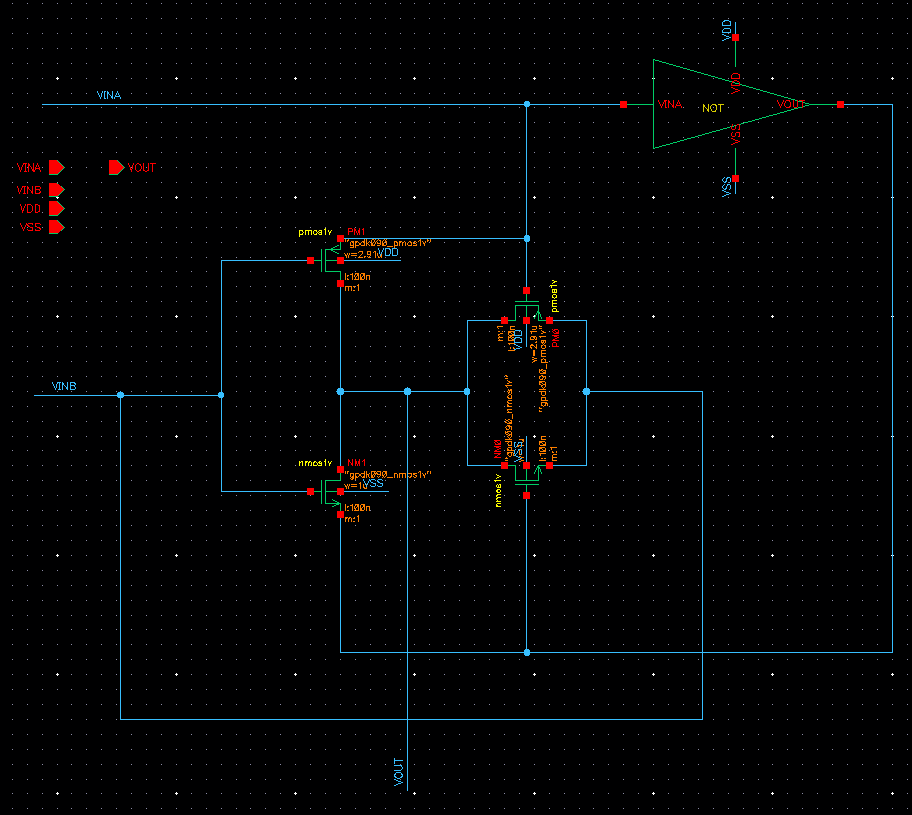

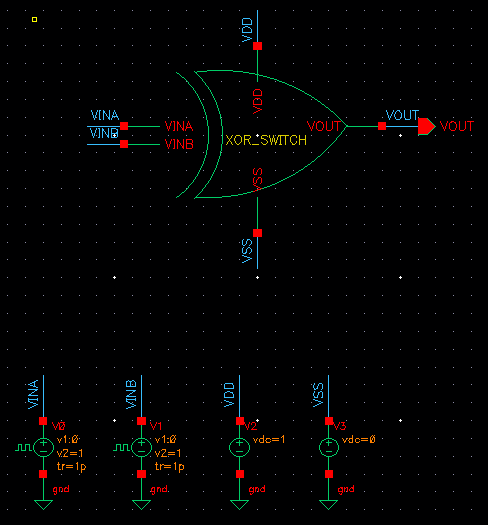

XOR(Switch)

Schematic

Stick Diagram

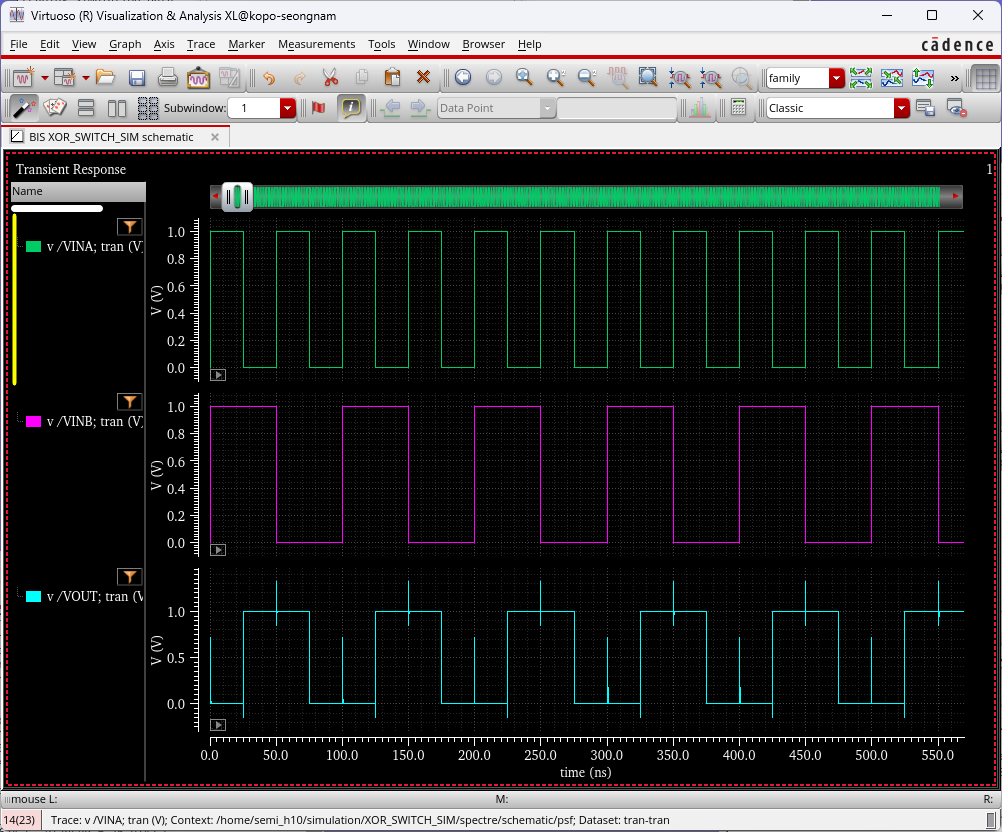

Simulation

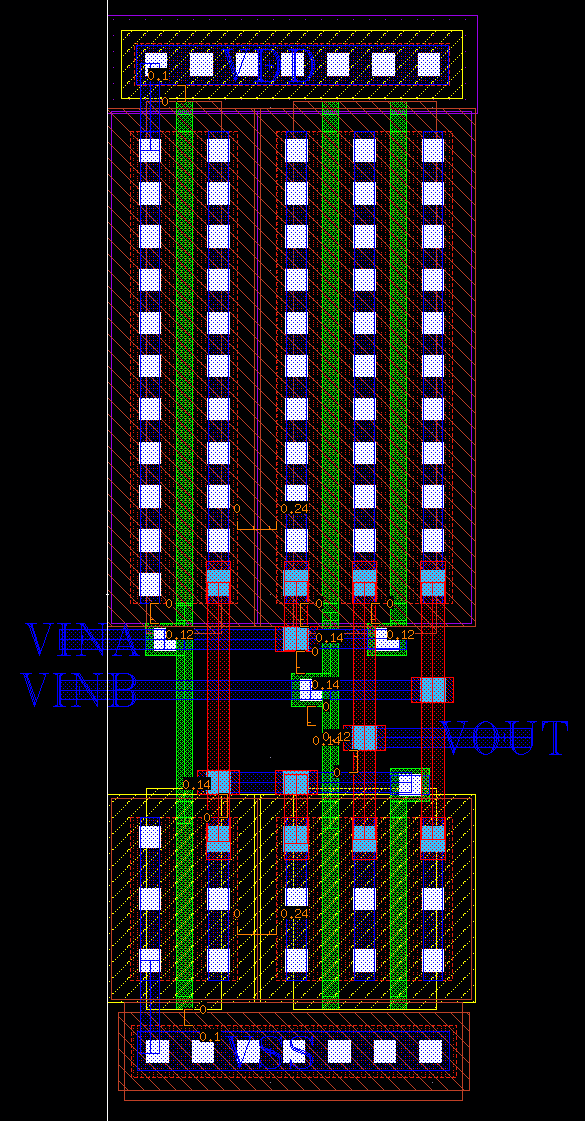

Layout

728x90

'Semiconductor > PCB, Virtuoso' 카테고리의 다른 글

| Virtuoso - MOS 구성 요소, Stick Diagram, Transmission Gate, QRC (0) | 2024.08.29 |

|---|---|

| Virtuoso - CS_AMP, Diff_AMP (0) | 2024.08.29 |

| Virtuoso - 2NAND / 2NOR (Schematic ~ Layout) (0) | 2024.08.26 |

| Virtuoso - 기본 Tool 사용법 + Inverter 만들기 (Schemetic ~ LVS) (0) | 2024.08.26 |

| PCB - up_down_controller 설계 4 (PCB 설계) (0) | 2024.04.15 |