CS_AMP, Diff_AMP

CS_AMP

일반적으로 MOSFET 또는 BJT를 사용하여 구성된다. 소스 단자가 접지에 연결된다.

cs_amp는 전압 이득이 매우 크며, 입력 신호에 비해 출력 신호를 크게 증폭할 수 있다.

입력 신호와 출력 신호의 위상이 180도 반전된다.

주파수 응답이 좋으며 고주파 신호에도 효과적이다.

Diff_AMP

두 개의 입력 단자가 있으며, 두 입력의 차이를 증폭한다.

두 입력의 전압 차이를 증폭하며, 공통 모드 신호(두 입력에 동시에 나타나는 신호)는 효과적으로 제거한다.

입력 임피던스가 높아 외부 회로에 미치는 영향이 적다.

신호 왜곡이 적고 안정성이 높다.

cs_amp는 주로 전압 증폭 및 신호 처리를 위해 사용되며, diff_amp는 차동 신호를 효과적으로 증폭하는 데 초점을 맞춘다.

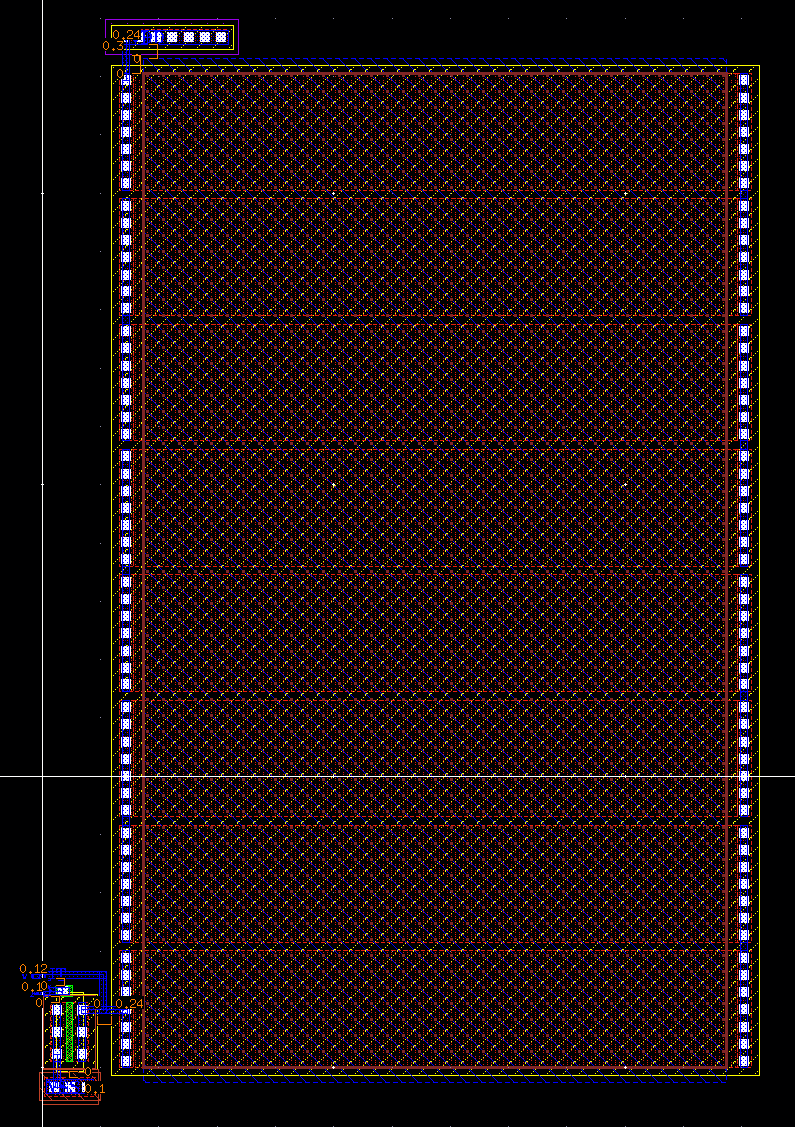

CS_AMP

Schematic

Simulation

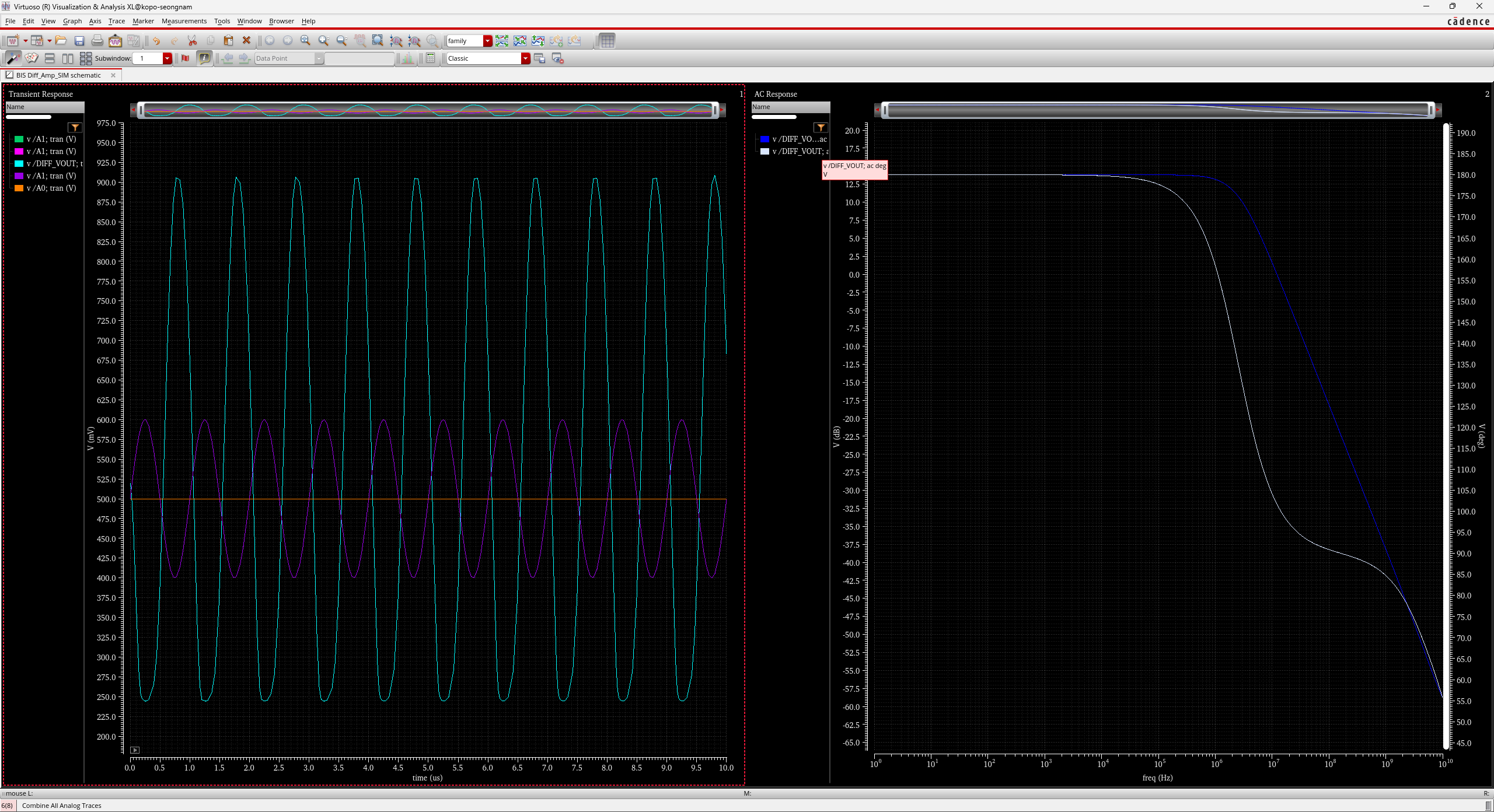

- Magnitude (이득 크기)

주파수에 따른 출력 신호의 크기를 보여준다. 전압 이득의 절대값을 주파수에 따라 나타낸 것이다.

주파수 대역에서 회로가 얼마나 큰 신호를 증폭할 수 있는지 보여준다.

- Phase (위상)

입력 신호와 출력 신호 사이의 위상 차이를 나타낸다. 이는 주파수에 따라 출력 신호가 입력 신호에 비해 얼마나 앞서거나 뒤처지는지를 보여준다.

회로의 안정성을 평가하는 데 중요하며, 특히 주파수 응답에서 위상 여유와 관련이 있다.

- db20 (이득 데시벨 단위)

이득을 데시벨 단위로 변환한 것으로, 주파수에 따른 이득의 상대적인 크기를 나타낸다.

특정 주파수에서 회로의 증폭 성능이 어떻게 변하는지 알 수 있으며, 회로의 대역폭을 분석하는 데 사용된다.

* 비교하는 이유

안정성 분석, 대역폭 평가, 전체적인 주파수 응답 분석

안정성 분석 : Magnitude와 Phase를 함께 보면, 특정 주파수에서 회로의 안정성을 평가할 수 있다.

대역폭 평가 : db20과 Magnitude 그래프를 비교하면 회로의 대역폭을 알 수 있다. 이득이 3dB 감소하는 지점을 통해 회로의 유효 대역폭을 결정할 수 있다.

Layout

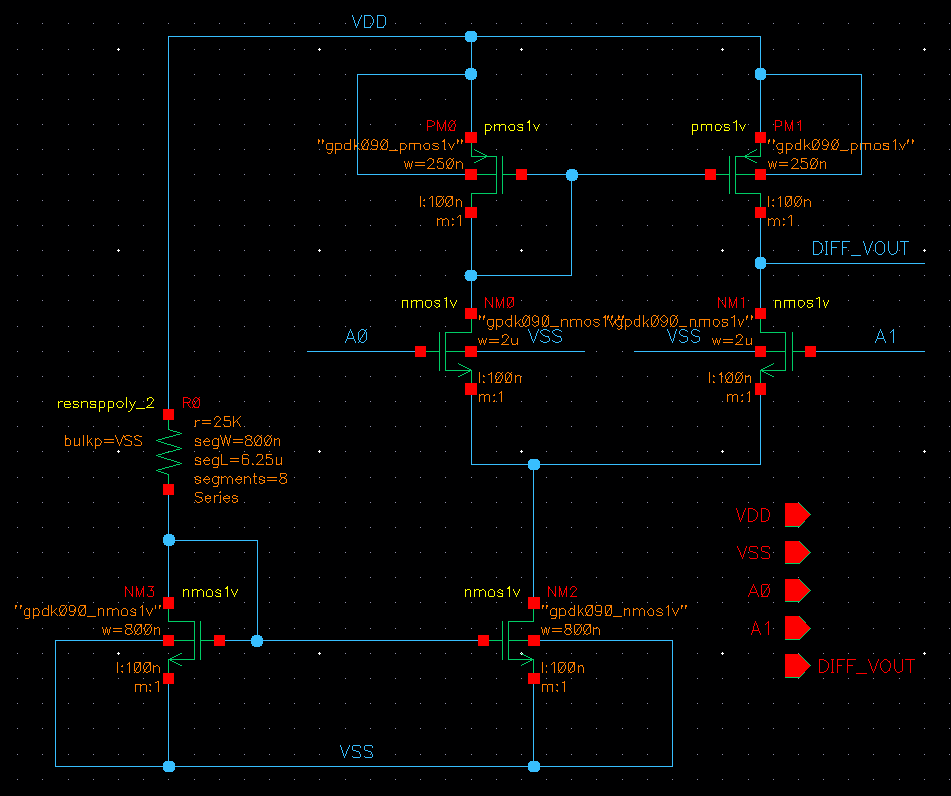

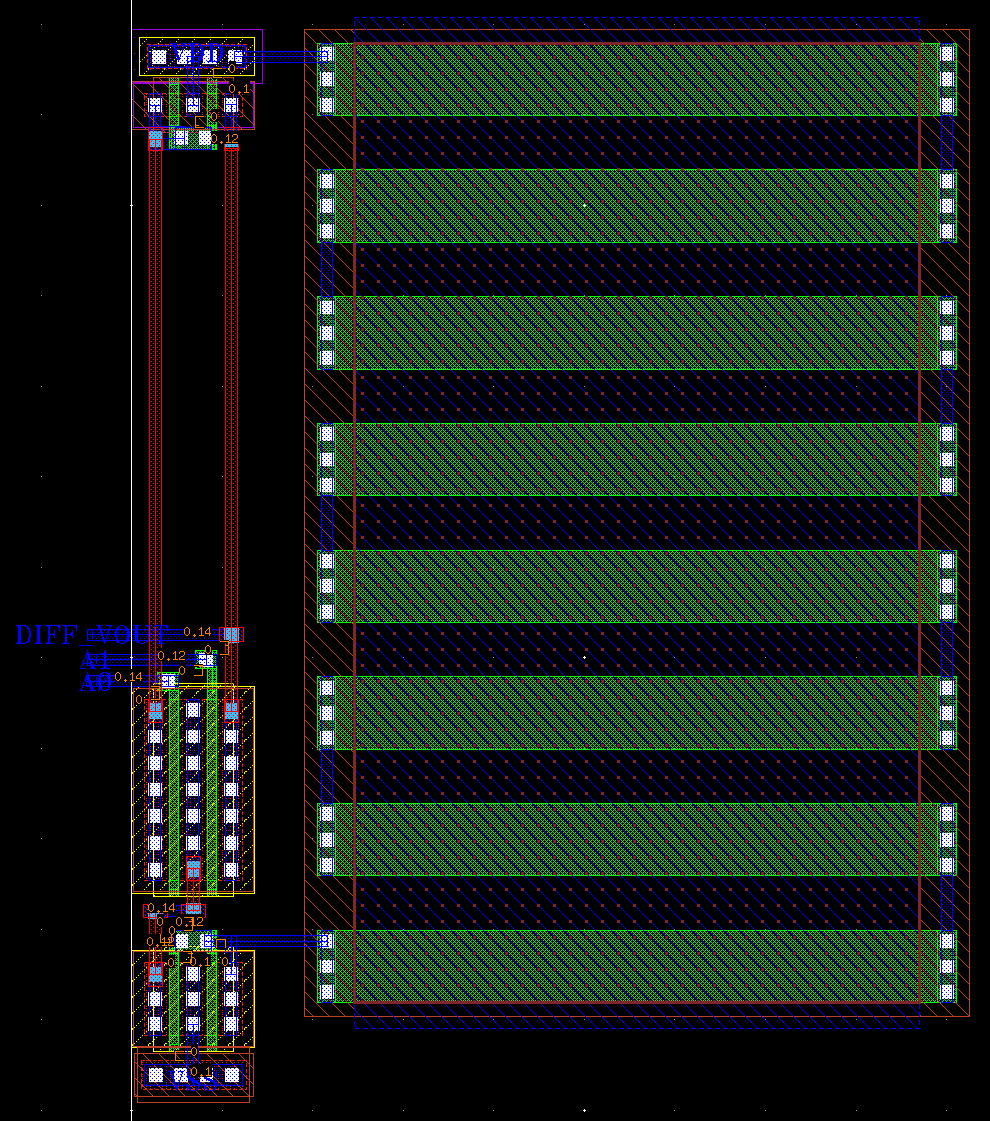

Diff_Amp

Schematic

Simulation

Layout

'Semiconductor > PCB, Virtuoso' 카테고리의 다른 글

| Virtuoso - Half Adder / Full Adder (0) | 2024.08.30 |

|---|---|

| Virtuoso - MOS 구성 요소, Stick Diagram, Transmission Gate, QRC (0) | 2024.08.29 |

| Virtuoso - 2x1 MUX(Logic, Switch) / XOR(Logic, Switch) (0) | 2024.08.27 |

| Virtuoso - 2NAND / 2NOR (Schematic ~ Layout) (0) | 2024.08.26 |

| Virtuoso - 기본 Tool 사용법 + Inverter 만들기 (Schemetic ~ LVS) (0) | 2024.08.26 |