Half Adder

| A | B | SUM | CARRY |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Half Adder의 진리표를 보게되면 SUM의 경우 XOR, Carry의 경우 AND Gate와 동일한 것을 볼 수 있다.

기존에 생성한 Symbol을 이용하여 Half Adder를 생성할 수 있다.

Schematic

Simulation

Simulation을 보게되면 진리표와 같이 SUM과 CARRY의 신호가 정상적으로 나오는 것을 확인할 수 있다.

Layout

기존의 XOR, NAND, NOT Layout을 이용하여 Half Adder Layout을 쉽게 설계할 수 있다.

Full Adder

| VINA | VINB | CIN | SUM | CARRY |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

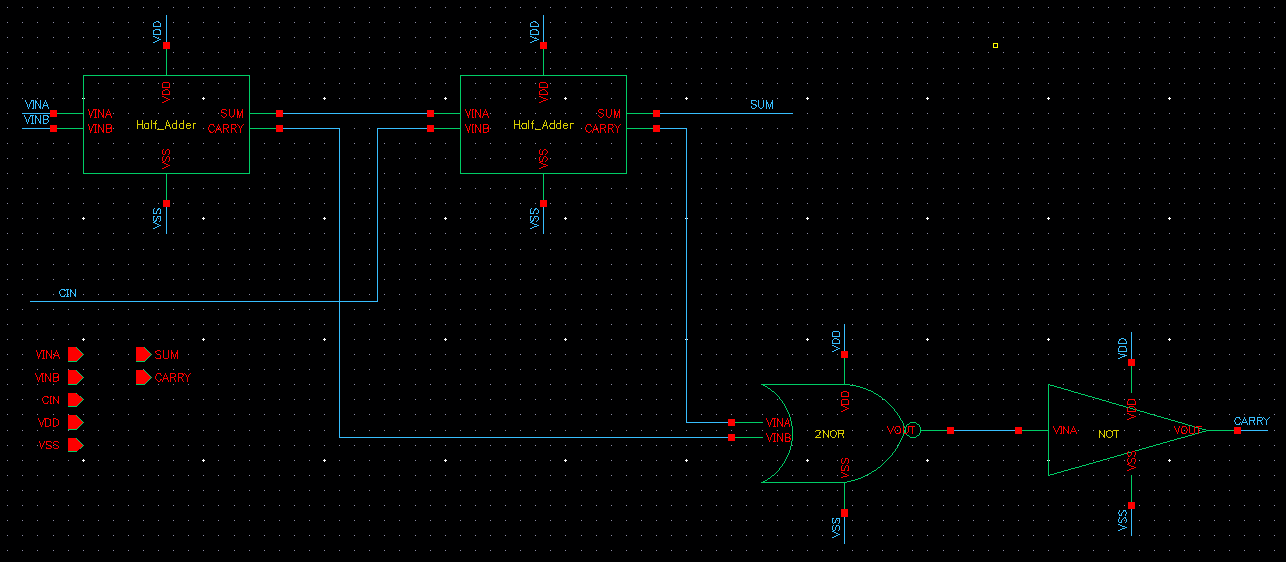

Schematic

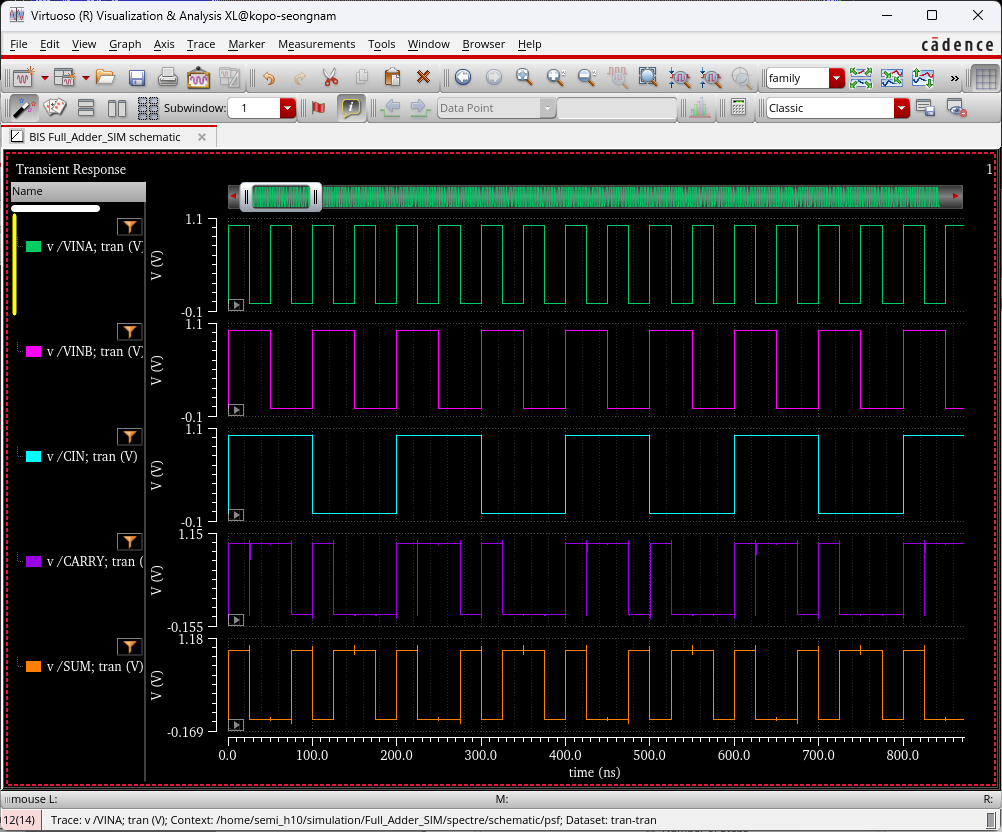

Simulation

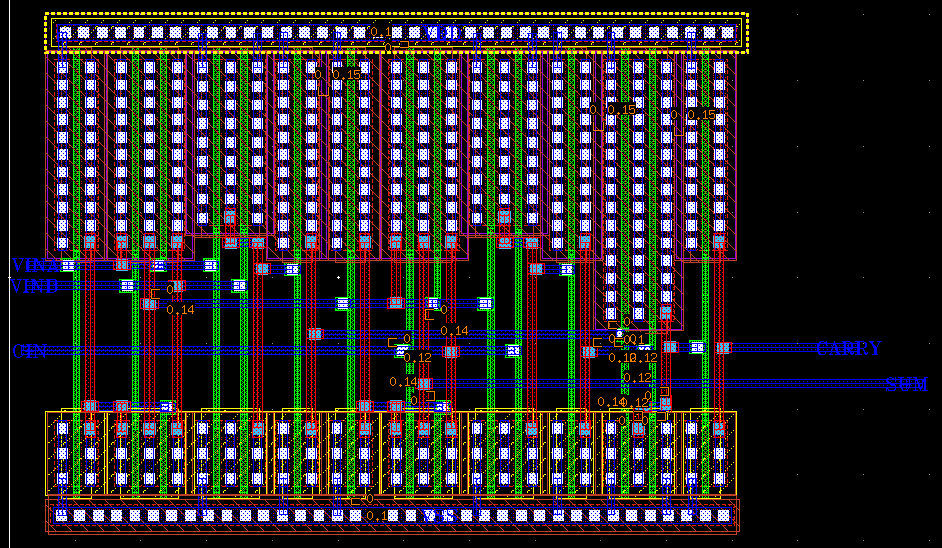

Layout

728x90

'Semiconductor > PCB, Virtuoso' 카테고리의 다른 글

| Virtuoso - 4x1_Mux (Logic, Switch) (0) | 2024.09.03 |

|---|---|

| Virtuoso - 4_Bit_Full_Adder (0) | 2024.09.02 |

| Virtuoso - MOS 구성 요소, Stick Diagram, Transmission Gate, QRC (0) | 2024.08.29 |

| Virtuoso - CS_AMP, Diff_AMP (0) | 2024.08.29 |

| Virtuoso - 2x1 MUX(Logic, Switch) / XOR(Logic, Switch) (0) | 2024.08.27 |