https://insoobaik.tistory.com/676

https://insoobaik.tistory.com/677

이전 FIFO 구조 및 동작 원리 이론에 이어서 실제 FIFO 이론을 RTL 설계를 할 것이다.

기본적인 FIFO 구조 설계는 FIFO Buffer에 대해 Async 비동기로 Data를 Write, Read하게 된다.

1. FIFO Buffer의 Data Full, Empty에 대한 Flag가 필요하다.

2. Write, Read가 비동기로 이루어지기 때문에 FIFO Buffer에 있는 데이터의 위치를 확인하기 위한 각각의 Write, Read Pointer가 필요하다.

3. 위 FIFO에 대한 이론 글에서 봤듯이 Pointer Data 손실을 방지하기 위해 Gray Code로 변경하는 코드가 필요하다.

추가로 FIFO 설계에 있어서 위 이론에서도 설명했듯이 CDC에 주의하여 설계해야 한다.

위와 같이 Write, Read에 대한 Clock이 다른 상태에서 위와 같이 Clock Edge 구간이 중복되는 순간이 발생할 수 있다. 해당 구간에서 Data가 Write, Read가 동시에 이루어지면 불안정한 Data(Metastability)가 전달될 수 있고 Data 손실이 일어나 큰 결함을 일으킬 수 있다.

추가로 Write Pointer가 Read Clock에 Read Pointer가 Write Clock에 맞게 Data를 확인할 수 있도록 Clock에 대한 Pointer를 추가로 생성하여 Metastability가 발생하지 않도록 중간에 Flip Flop을 하나 더 생성하여 Data를 저장하도록 구성한다.

Write Pointer는 Read Clock에 Read Pointer는 Write Clock에 대한 별도의 변수를 생성하는 이유는 위에서 얘기했지만 비동기로 동작하기 때문에 Full, Empty에 대한 정보가 확실해야 하기 때문에 Clock 속도가 다른 상태에서 상대방의 Clock에 맞게 Data를 확인해야 하는 작업이 필요하기 떄문이다.

CDC 방지를 위한 설계

always @(posedge wclk or negedge rstn) begin

if (!rstn) begin

rptr_gray_meta <= 0;

rptr_gray_wclk <= 0;

end else begin

rptr_gray_meta <= rptr_gray;

rptr_gray_wclk <= rptr_gray_meta; //synchronizer

end

end

.......

always @(posedge rclk or negedge rstn) begin

if (!rstn) begin

wptr_gray_meta <= 0;

wptr_gray_rclk <= 0;

end else begin

wptr_gray_meta <= wptr_gray;

wptr_gray_rclk <= wptr_gray_meta;

end

end

위 코드가 metastability가 발생하지 않기 위해 meta라는 Flip Flop을 하나 더 추가하여 Data를 저장한다.

추가로 Read Clock에 대한 Wirte Pointer, Write Clock에 대한 Read Pointer 변수를 생성하여 Pointer 값을 저장한다.

메모리 초기화 및 Push Flag에 의한 Data 저장

// WCLK DOMAIN

always @(posedge wclk or negedge rstn) begin

if (!rstn) begin

for (i = 0; i < DEPTH; i = i + 1) begin

mem[i] <= 0;

end

end else if (push & ~full) begin

mem[wptr_bin[DEPTH_LOG-1:0]] <= din;

end

end

처음 rstn 신호가 1이 되고 난 뒤din을 통해 Data가 들어가게 되고, wclk에 맞춰 Data가 Push 된다.

Empty Flag

assign empty = (rptr_gray == wptr_gray_rclk);

wptr_gray_rclk(Read 클럭에 따른 Write Gray Code)값과 rptr_gray(Read Gray Code)값이 같을 때만 FIFO Buffer가 비어있는 상태이기 때문에 Pointer의 값이 달라지면 Empty Flag가 Low로 변경된다.

Full Flag

assign full = (wptr_gray[DEPTH_LOG-:2] == ~rptr_gray_wclk[DEPTH_LOG-:2]) &&

(wptr_gray[DEPTH_LOG-2:0] == rptr_gray_wclk[DEPTH_LOG-2:0]);

(* 이전 FIFO 관련 이론 글 참조)

FIFO Buffer에서 Gray Code를 통해 Data 위치를 지정하기로 하였다. (Full과 Empty를 구분하기 위하여)

Write Clock에 맞춰 동작하는 Read Pointer의 값과 실제 Write Pointer 값을 비교하였을 때 (위에서도 설명했지만 Read Pointer는 Write Clock에 맞춰 확인해야 CDC를 피할 수 있다.) 하위 2비트의 값이 같고(실제 Buffer의 위치) 상위 2비트의 값이 반전(해당 자리가 한바퀴 돌고 난 후 자리인지 아닌지 비교하는)되었으면 Full임을 인시가혹 Full Flag를 High로 변경한다.

Pop에 의한 Data 출력

always @(posedge rclk or negedge rstn) begin

if (!rstn) rptr_bin <= 0;

else if (pop & ~empty) rptr_bin <= rptr_bin + 1;

end

...

assign empty = (rptr_gray == wptr_gray_rclk);

assign dout = mem[rptr_bin[DEPTH_LOG-1:0]];

Empty Flag가 High가 아닐 때 Pop 신호가 High일 경우 rptr_bin의 값을 가지고 FIFO Buffer의 위치를 지정한다.

여기서 Gray Code를 사용하지 않고 FIFO Buffer의 Pointer 값을 bin값을 통해 찾는 것을 볼 수 있다.

(이전 FIFO 이론 글을 참고) FIFO에서 Gray Code는 Full, Empty를 비교하기 위한 값이였다.

FIFO Buffer 주소는 Binary 이진수로 관리되기 때문에 Buffer에 직접 접근할 때는 Binary를 통해 접근해야 한다.

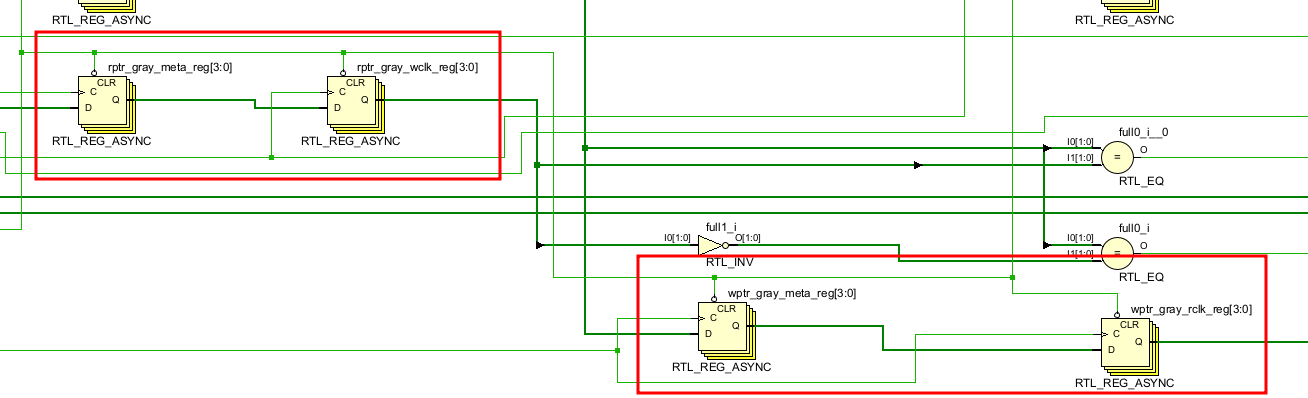

Schematic

MetaStability

Synthesis 이후 Schematic을 확인해보면 Metastability를 방지하기 위한 추가 Flip Flop을 거친 뒤 다음 D Flip Flop으로 Data가 전달되는 것을 확인할 수 있다.

추가로 2차원 Memory를 Mux를 통해 접근하여 실제 Data가 저장되는 8 bit Register의 활성화를 결정 짓고 있는 것을 확인할 수 있다.

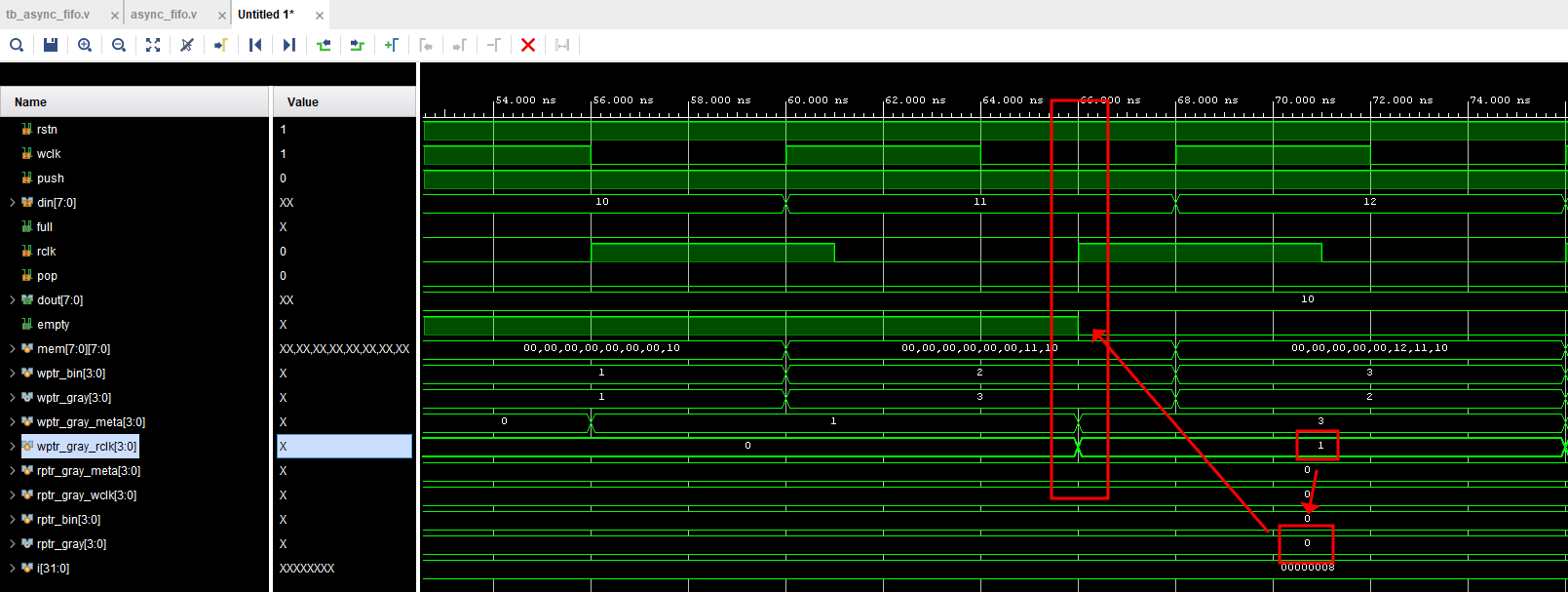

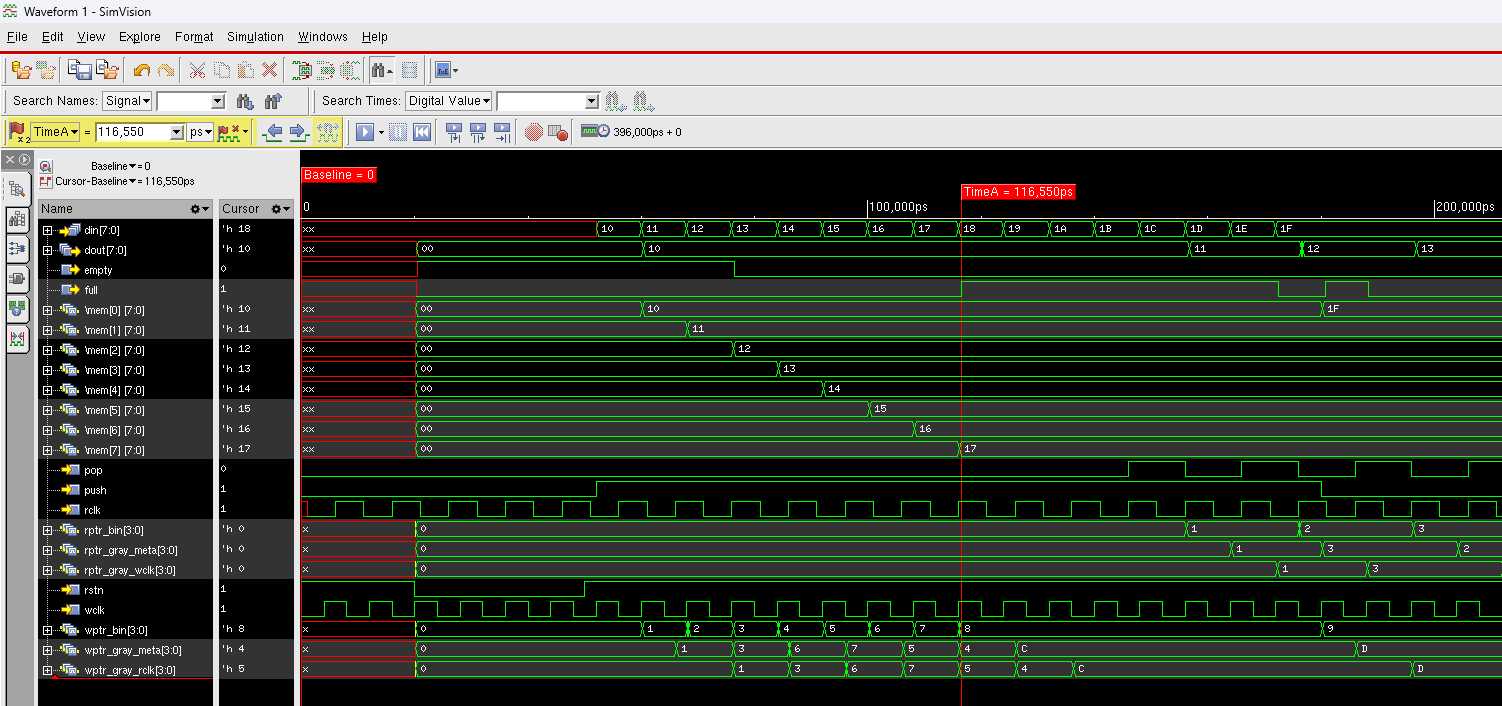

Pre_Layout Simulation

Synthesis 이후 Delay가 적용된 Pre_Layout Simulation을 확인할 수 있다. 아직 물리적 배선이 되기 이전의 Simulation이기 때문에 Gate Level에서 실행된 Simulation이다.

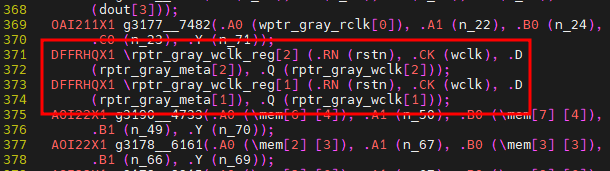

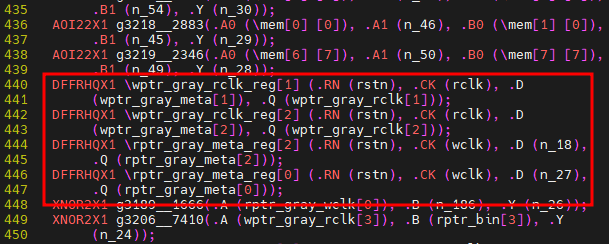

Netlist에 생성된 metastability 방지를 위한 DFF

Synthesis 이후 Netlist를 통해 Metastability를 해결하기 위한 D Filp Flop이 생성된 것을 확인할 수 있다.

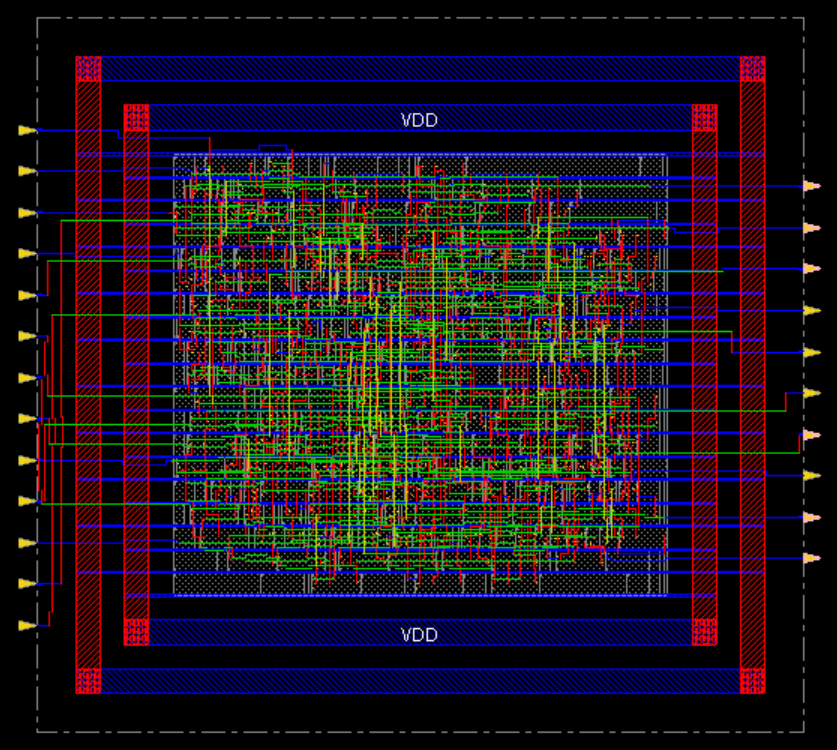

PnR

Auto PnR을 통해 Logic 수준이 아닌 실제 물리적 Place & Routing을 마친 뒤 Netlist, SDF, GDSII 파일이 생성된다.

PnR 이후 생성된 Netlist와 SDF 파일을 통해 Post_Layout Simulation을 통해 이상이 없는지 확인한다.

최종적으로 이상이 없을경우 GDSII 파일을 공정사에 전달한다.

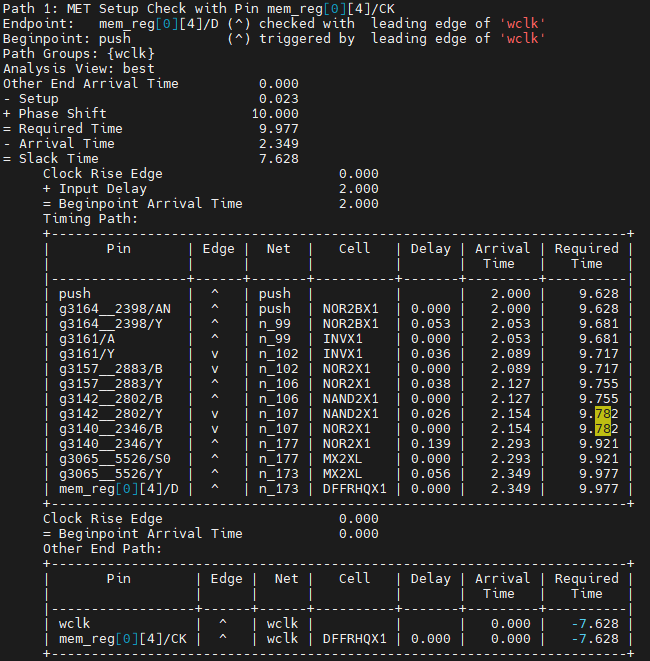

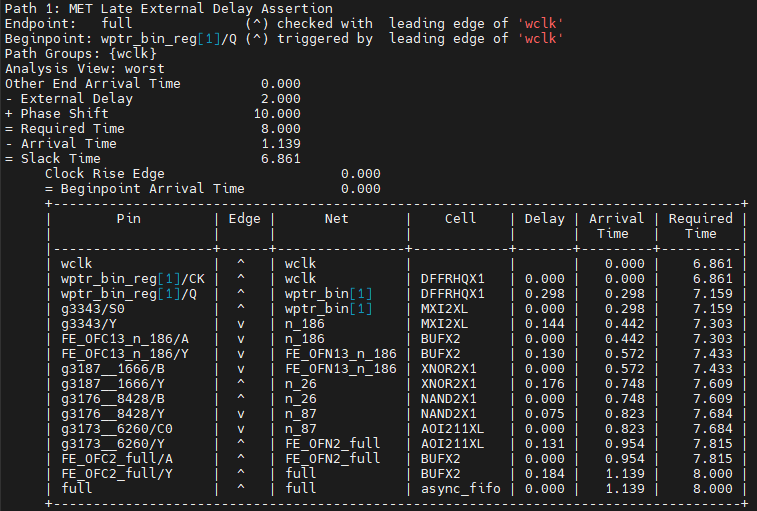

Timing Report

신호가 전파되는 시간을 분석하는 Timing Report를 통해 신호가 제 시간안에 도달했는지 확인하게 된다.

Setup, Hold Time과 같은 타이밍 요구 사항이 충족 되는지 확인하며, Slack Time이 양수일 경우 요구 시간 안에 신호가 도착했음을 알 수 있다.

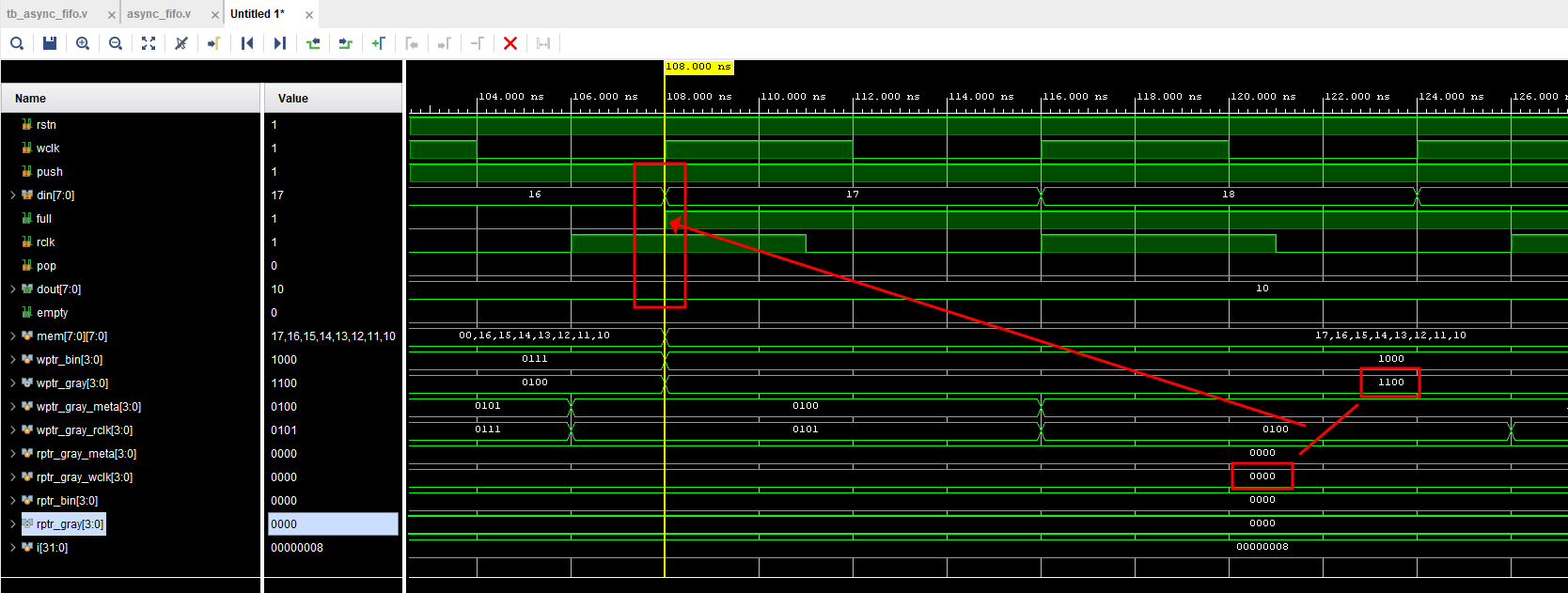

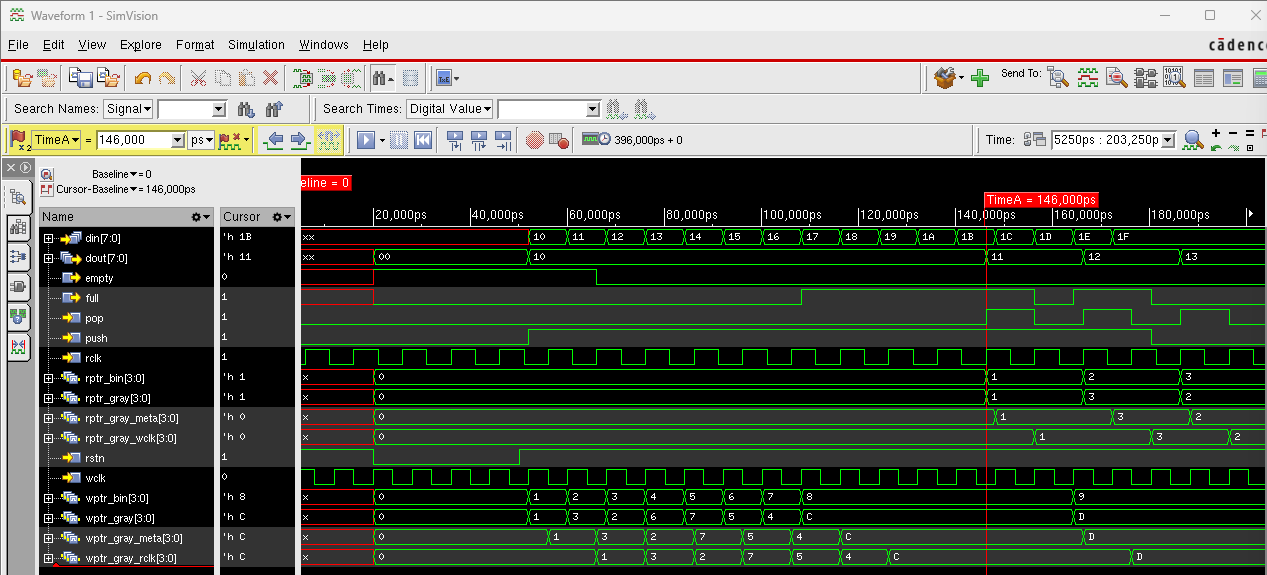

Post_Layout Simulation

실제 물리적 Place & Routing이 적용된 Netlist, SDF 파일을 통해 Delay가 적용된 Post_Layout Simulation을 위와 같이 확인할 수 있다.

Result

Pre_Layout Simulation

Post_Layout Simulation

Pre, Post_Layout Simulation을 비교하게 되면 간단한 위 Simulation을 예로 첫번째 Pop 신호에 대해 Pre는 신호를 출력하고, Post는 신호를 출력하지 못하고 다음 Pop 신호에 신호를 전달하는 것을 확인할 수 있다. 실제 물리적인 배치가 이루어지지 않고 논리적인 제약(Pre)에 의한 신호 전달과 실제 물리적인 배치가 이루어진 후의 신호 전달(Post)에 있어 확연한 차이가 발생하는 것을 확인할 수 있다.

'Semiconductor > 0. ASIC Flow' 카테고리의 다른 글

| ASIC Flow - SPI 설계, 신호 검증 (ILA) & (Cadence) Synthesis ~ POST SIM (0) | 2024.07.10 |

|---|