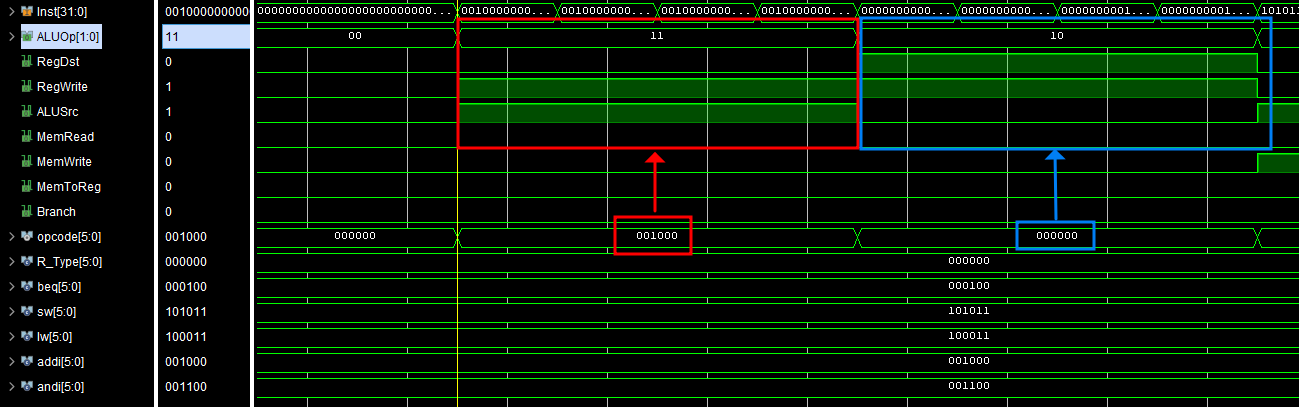

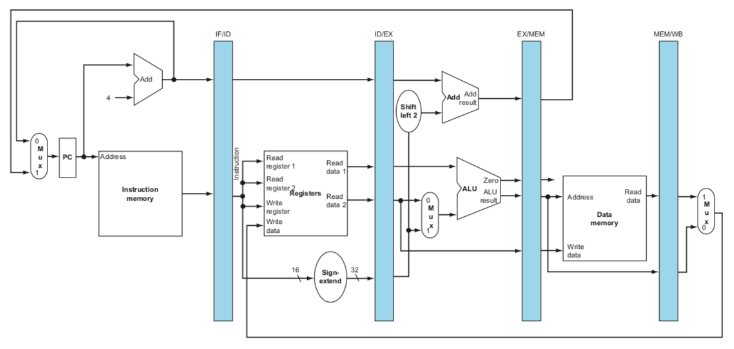

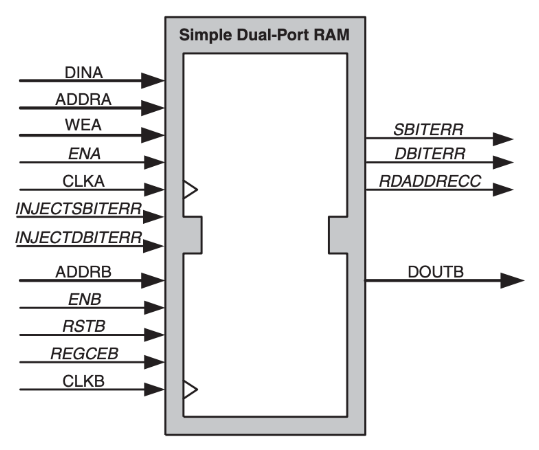

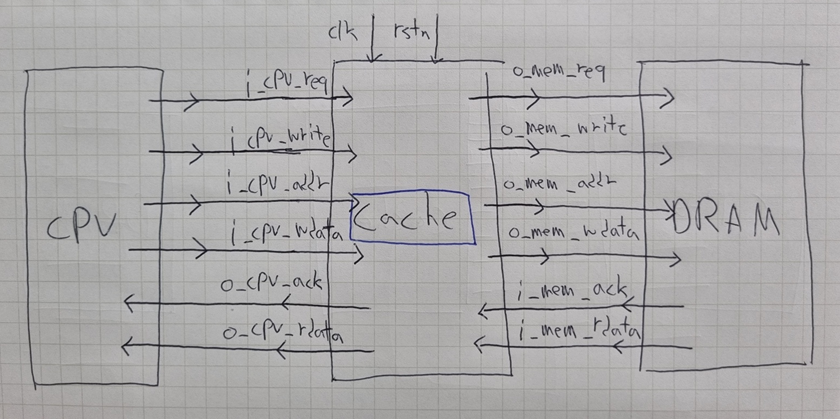

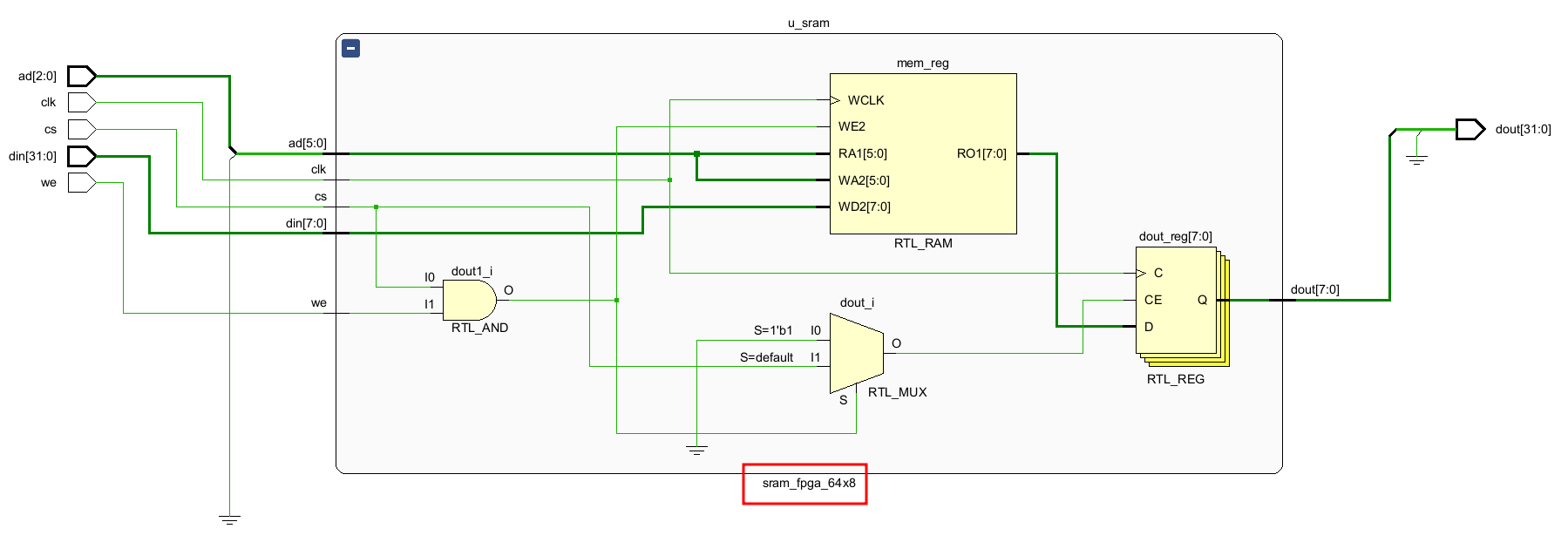

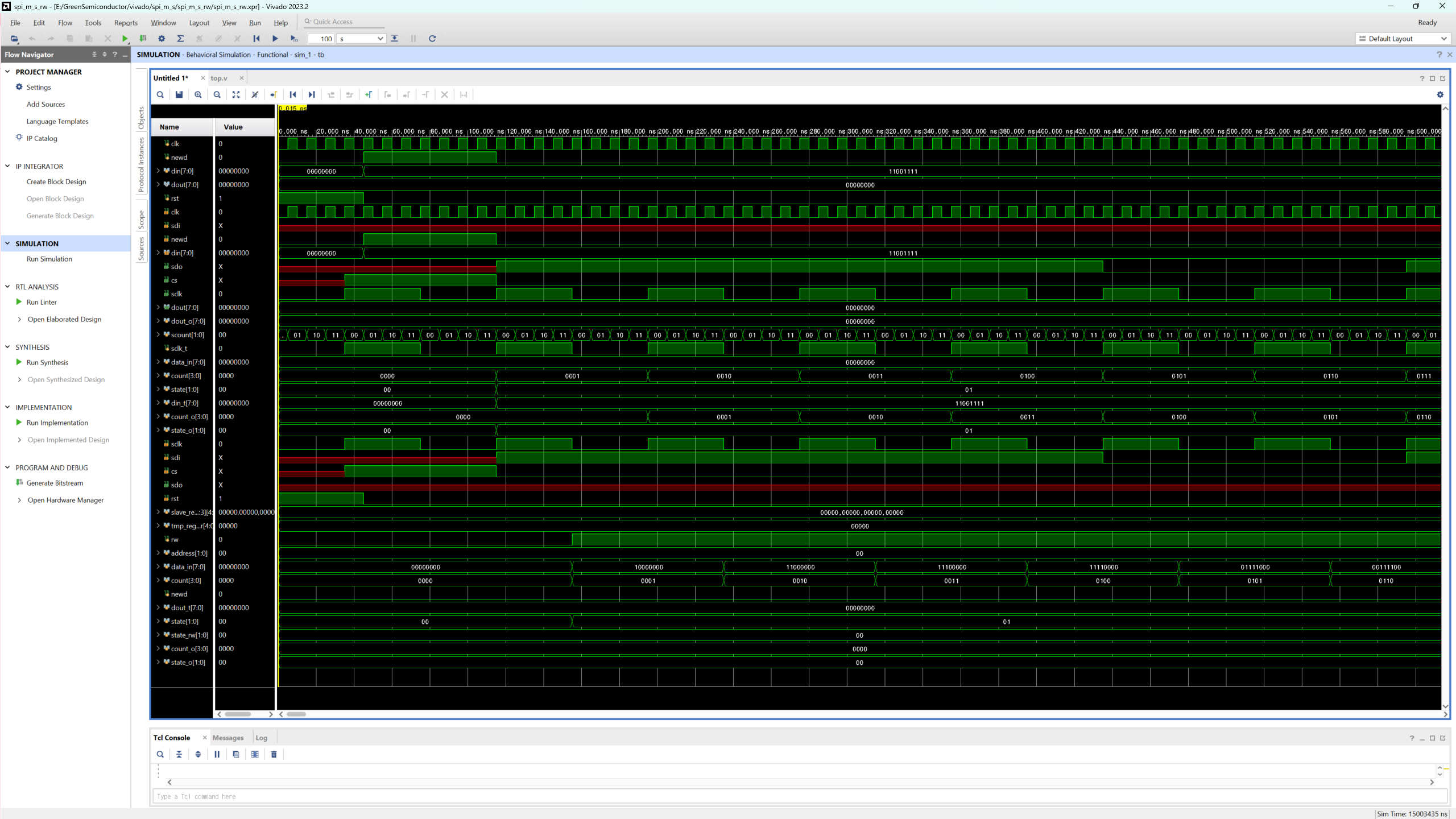

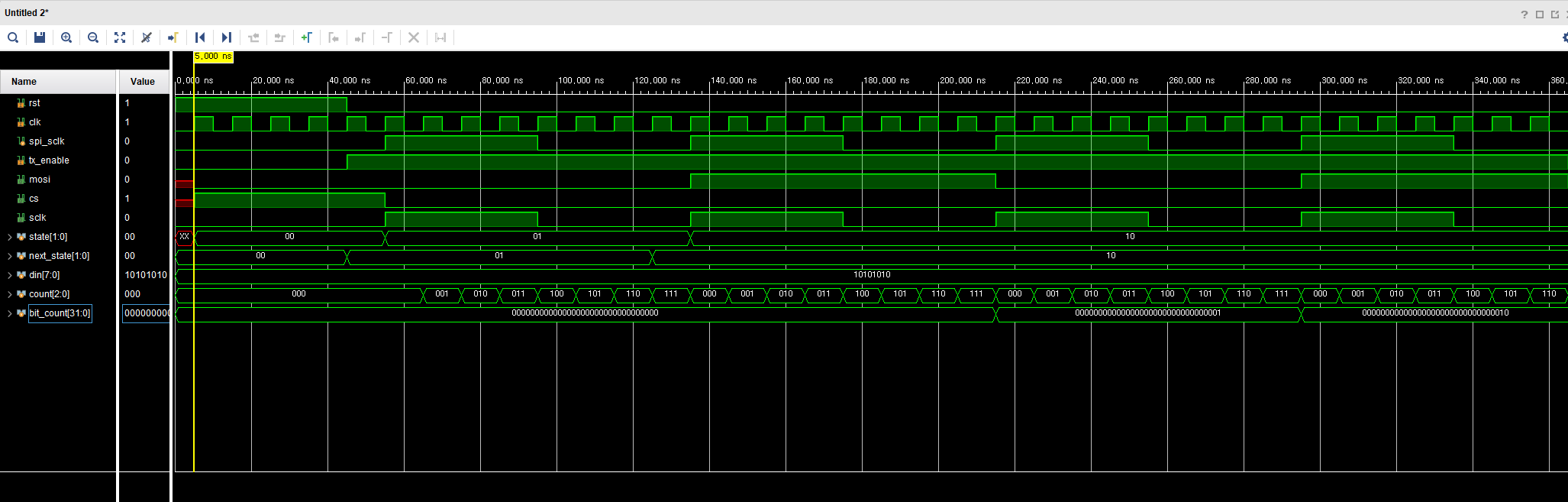

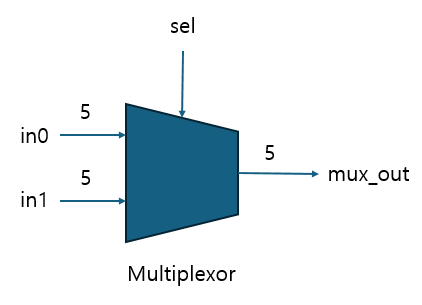

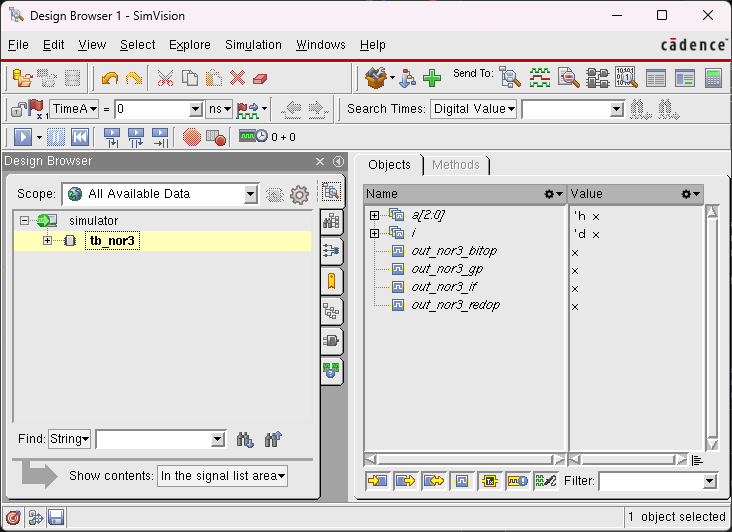

https://insoobaik.tistory.com/719 컴퓨터 구조 및 CPU 동작 원리 (3) - 32 Bit RISC CPU(Pipeline) RTL 설계https://insoobaik.tistory.com/717 컴퓨터 구조 및 CPU 동작 원리 (1) - 기본 개념목차컴퓨터의 구성요소 5가지Absractions and ISADefining PerformanceInstruction SetMIPS Arithmetic OperationRegister OperandsMemory OperandsImmediate Opeinsoobaik.tistory.comRTL 설계에 이어서 Simulation 분석을 해 볼 것이다.Schematic빨간색은 D/FF Reference를 포함한 InstMem, Contr..