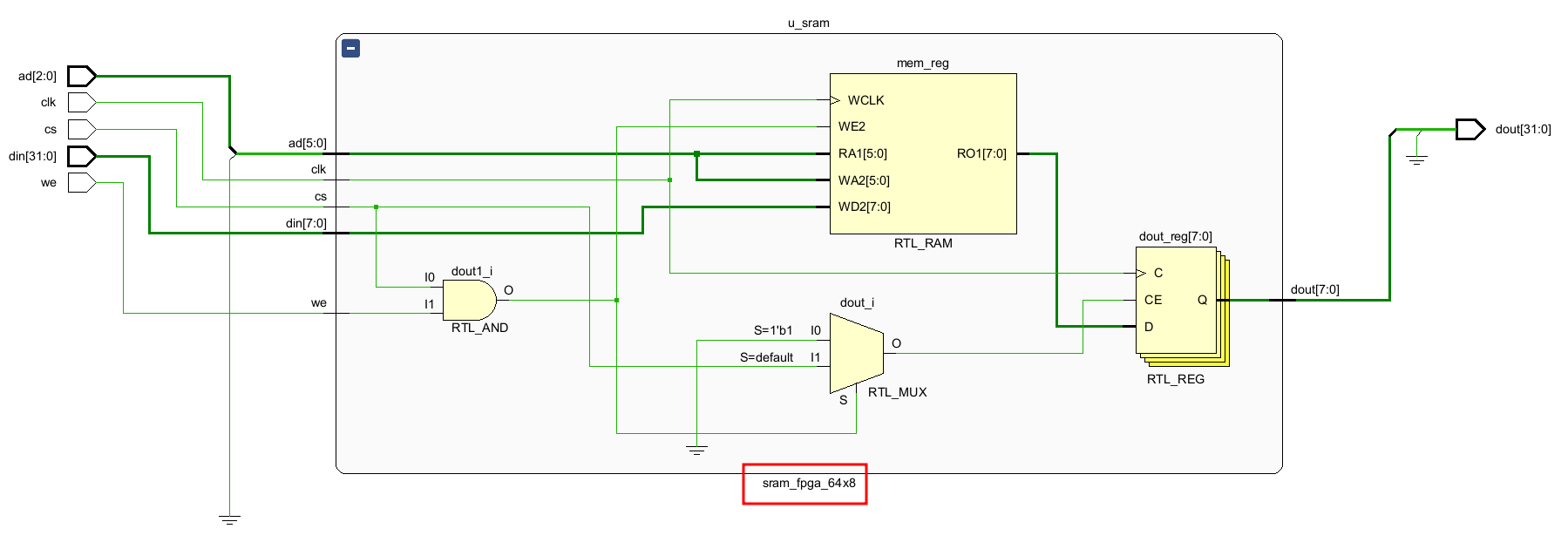

https://insoobaik.tistory.com/660 SRAM 구조 및 동작 원리보호되어 있는 글입니다. 내용을 보시려면 비밀번호를 입력하세요.insoobaik.tistory.comSRAM에 대한 내용은 위 글을 참고한다.■ SRAM SRAM은 기본적으로 clock, cs, we, ad, din, dout Pin을 가지게 된다. - clock : 동기화를 위해 사용된다.- cs : Chip Select로 해당 칩을 동작 시킬것인지 정하게 된다. High 신호에 동작하는 경우, cs가 1(High)일 때 만 Read, Write 행위가 가능하다.- we : Write Enable로 해당 메모리에 Read할 것인지 Write할 것인지 정하게 된다 (ex we 신호가 0일 경우 Read, we 신호가 ..