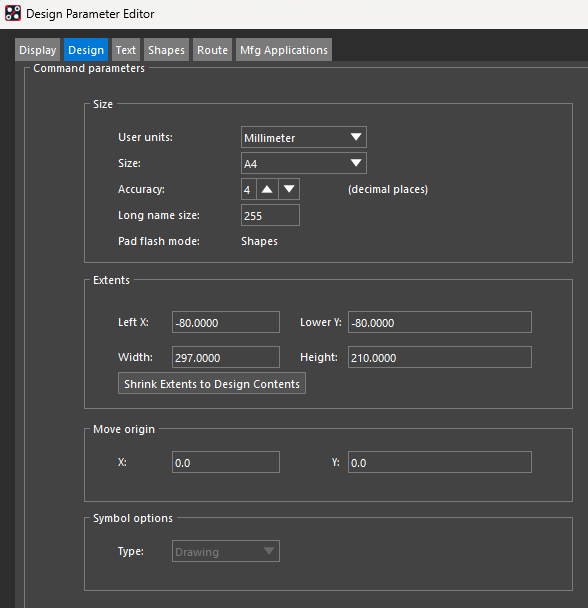

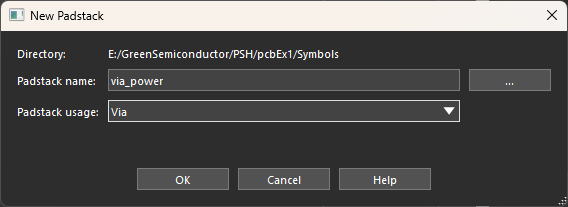

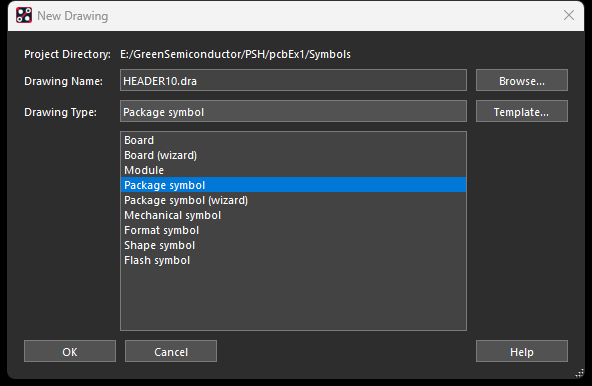

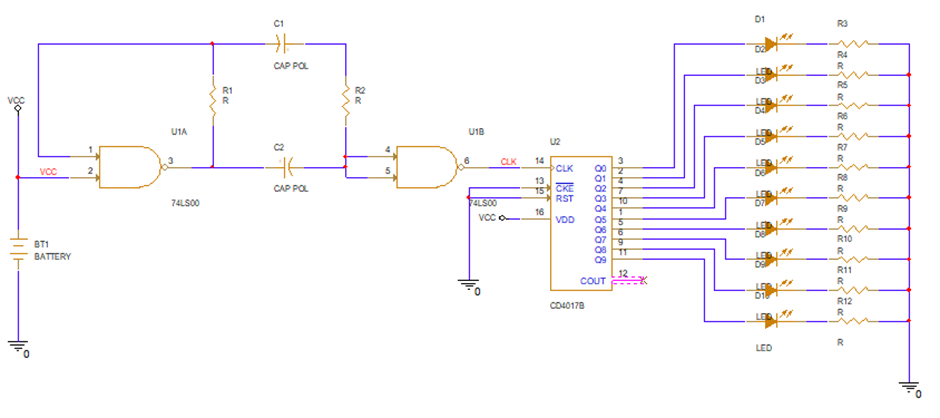

Design 탭 - Shapes 탭 Gerber 설정 ▶ Thru pins (스루홀의 단열판 연결 타입) : Orthogonal ▶ Minimum connects (단열판의 최소 연결선의 수) : 1 ▶ Use fixed width oversize of (단열판과 네트 사이의 연결선의 두께 설정) : 0. Grid 설정 Non-Etch의 경우 보드 외각선등 동박 영역 이외의 작성 시 사용되는 Grid이며, All Etch(TOP, BOTTOM)의 경우 전기적 접속을 이루는 동박 영역에서의 작업 Grid, 즉, 배선, 카퍼 작업 시 Grid를 설정할 수 있다. Layer 설정 보드외곽선 생성 - 기구 홀 및 주요 부품 배치하기 주요 부품 배치 - 치수보조선 치수보조선 그리기 - 실크 데이터 작성 Text ..