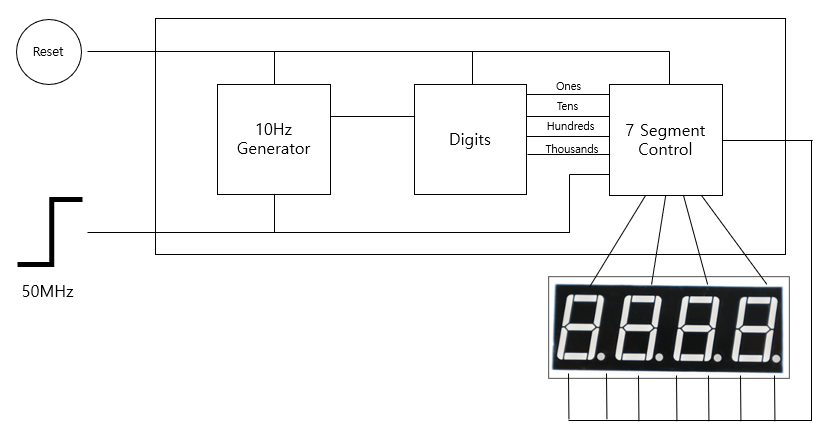

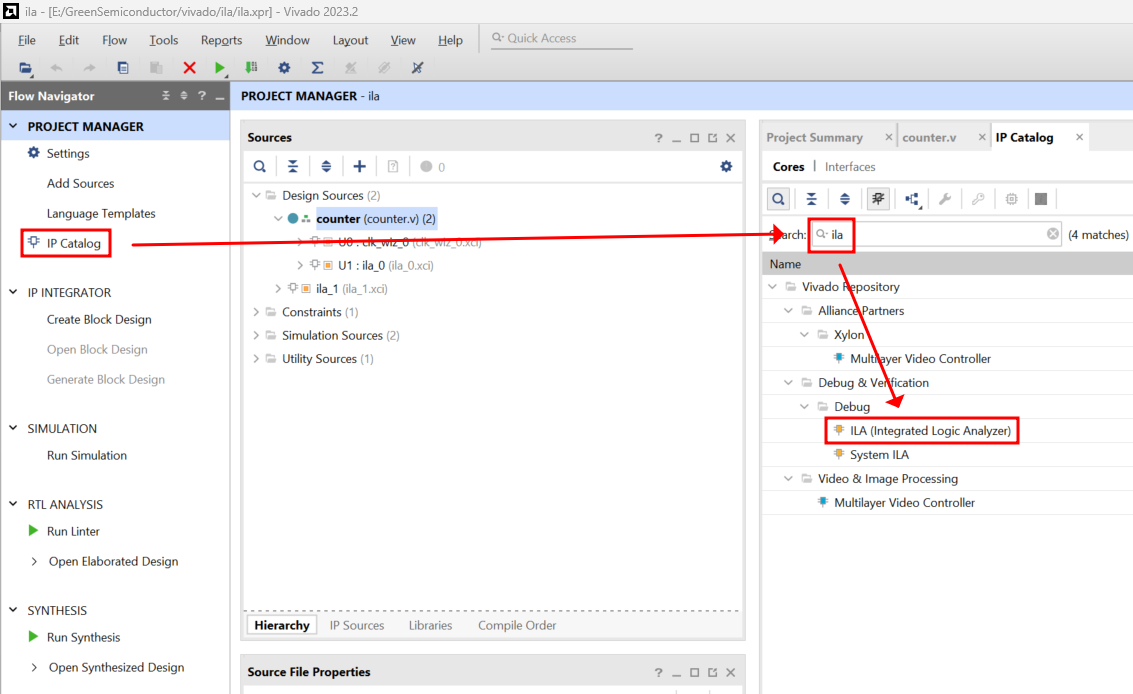

https://insoobaik.tistory.com/711 이전 글을 통해 Vivado에서 제공하는 AXI4-Lite Interface를 알아보았다. 이번 시간에는 AXI4-Lite를 이용하여 PS(Vitis)에서 값을 입력하면 해당 Freq가 PL(FPGA)의 Clock 모듈의 Clock으로 동작하여 시계가 동작하도록 구현할 것이다.* Clock의 경우 100MHz를 사용한다. Block Diagram Watch_Top.v먼저 시계를 담당하는 Module의 경우 Input- clk- rst- run_en : HIGH일 때 시계 동작- freq : 현재 Clock이 100MHz이고, 입력 freq를 설정하여 시계의 속도를 조절한다. (freq = 100000000일 경우 1초에 해당한다.) Output..