https://insoobaik.tistory.com/622

Innovus - P&R (SETUP ~ GDSII)

보호되어 있는 글입니다. 내용을 보시려면 비밀번호를 입력하세요.

insoobaik.tistory.com

이전에 P&R 작업을 GUI를 통해 작업한 바가 있다.

매번 위 과정을 계속해서 반복해야 한다면 시간이 오래 걸릴 수도 있고, 중간에 실수가 발생할 수 있기 때문에 Script 파일을 생성하여 동작 시키는 것이 시간과 안정성에 있어서 좋다.

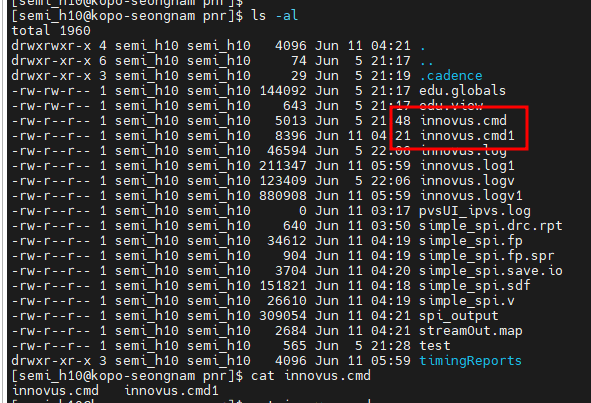

innovus를 실행하게 되면 기본 생성 파일로 1. 로그 파일 2. 명령 파일이 생성되는 것을 알고 있다.

innovus.cmd 파일을 확인해보면 GUI를 통해 진행한 P&R에 대한 명령어가 기록되어 있는 것을 확인할 수 있다.

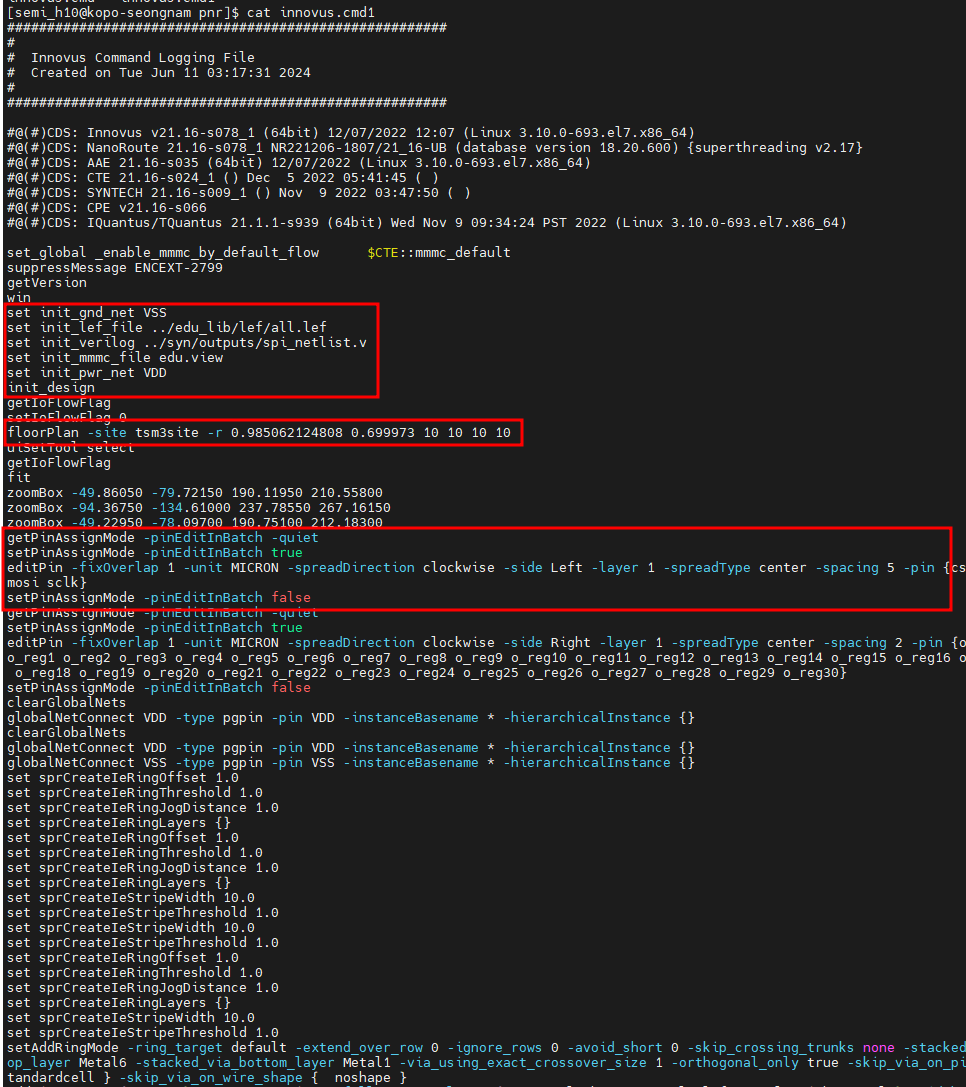

innovus.cmd 파일을 열어보게 되면 위와 같이 GUI를 통해 수행한 동작과 입력한 값에 따라 실제 적용된 명령어들이 나열되어 있는 것을 확인할 수 있다.

위 파일을 참고하여 실제 수행을 위한 명령어를 구분하여 별도의 스크립트 파일을 생성한다.

(GUI에서 한단계식 수행하고 생성되는 명령어를 Script 파일에 옮기는 것이 수월한 것 같다.)

#Setup

set init_gnd_net VSS

set init_lef_file ../edu_lib/lef/all.lef

set init_verilog ../syn/outputs/spi_netlist.v

set init_mmmc_file edu.view

set init_pwr_net VDD

init_design

#Floor Plan

floorPlan -site tsm3site -r 0.985062124808 0.699973 10 10 10 10

#Pin

getPinAssignMode -pinEditInBatch -quiet

setPinAssignMode -pinEditInBatch true

editPin -fixOverlap 1 -unit MICRON -spreadDirection clockwise -side Left -layer 1 -spreadType start -spacing 5 -start 0.0 0.0 -pin {cs miso mosi sclk}

setPinAssignMode -pinEditInBatch false

getPinAssignMode -pinEditInBatch -quiet

setPinAssignMode -pinEditInBatch true

editPin -pinWidth 0.23 -pinDepth 0.23 -fixOverlap 1 -unit MICRON -spreadDirection clockwise -side Left -layer 1 -spreadType center -spacing 5 -pin {cs miso mosi sclk}

setPinAssignMode -pinEditInBatch false

getPinAssignMode -pinEditInBatch -quiet

setPinAssignMode -pinEditInBatch true

editPin -fixOverlap 1 -unit MICRON -spreadDirection clockwise -side Right -layer 1 -spreadType center -spacing 2 -pin {o_reg0 o_reg1 o_reg2 o_reg3 o_reg4 o_reg5 o_reg6 o_reg7 o_reg8 o_reg9 o_reg10 o_reg11 o_reg12 o_reg13 o_reg14 o_reg15 o_reg16 o_reg17 o_reg18 o_reg19 o_reg20 o_reg21 o_reg22 o_reg23 o_reg24 o_reg25 o_reg26 o_reg27 o_reg28 o_reg29 o_reg30}

setPinAssignMode -pinEditInBatch false

#Power

globalNetConnect VDD -type pgpin -pin VDD -instanceBasename * -hierarchicalInstance {}

globalNetConnect VSS -type pgpin -pin VSS -instanceBasename * -hierarchicalInstance {}

#Power Ring

setAddRingMode -ring_target default -extend_over_row 0 -ignore_rows 0 -avoid_short 0 -skip_crossing_trunks none -stacked_via_top_layer Metal6 -stacked_via_bottom_layer Metal1 -via_using_exact_crossover_size 1 -orthogonal_only true -skip_via_on_pin { standardcell } -skip_via_on_wire_shape { noshape }

addRing -nets {VDD VSS} -type core_rings -follow core -layer {top Metal1 bottom Metal1 left Metal2 right Metal2} -width {top 1.8 bottom 1.8 left 1.8 right 1.8} -spacing {top 1.8 bottom 1.8 left 1.8 right 1.8} -offset {top 1.8 bottom 1.8 left 1.8 right 1.8} -center 0 -threshold 0 -jog_distance 0 -snap_wire_center_to_grid None

#Power Route

setSrouteMode -viaConnectToShape { noshape }

sroute -connect { blockPin padPin padRing corePin floatingStripe } -layerChangeRange { Metal1(1) Metal6(6) } -blockPinTarget { nearestTarget } -padPinPortConnect { allPort oneGeom } -padPinTarget { nearestTarget } -corePinTarget { firstAfterRowEnd } -floatingStripeTarget { blockring padring ring stripe ringpin blockpin followpin } -allowJogging 1 -crossoverViaLayerRange { Metal1(1) Metal6(6) } -nets { VDD VSS } -allowLayerChange 1 -blockPin useLef -targetViaLayerRange { Metal1(1) Metal6(6) }

#Cell Place

setPlaceMode -fp false

place_design

#Check

checkPlace simple_spi.checkPlace

setDrawView place

#Pre_CTS ECO

setOptMode -fixCap true -fixTran true -fixFanoutLoad false

optDesign -preCTS

#Pre_CTS Report

redirect -quiet {set honorDomain [getAnalysisMode -honorClockDomains]} > /dev/null

timeDesign -preCTS -pathReports -drvReports -slackReports -numPaths 50 -prefix simple_spi_preCTS -outDir timingReports

#Route

setNanoRouteMode -quiet -routeTopRoutingLayer 6

setNanoRouteMode -quiet -routeBottomRoutingLayer 1

setNanoRouteMode -quiet -drouteEndIteration 1

setNanoRouteMode -quiet -routeWithTimingDriven false

setNanoRouteMode -quiet -routeWithSiDriven false

routeDesign -globalDetail

#Post_CTS ECO

setOptMode -fixCap true -fixTran true -fixFanoutLoad false

optDesign -postCTS

#Post_CTS Report

redirect -quiet {set honorDomain [getAnalysisMode -honorClockDomains]} > /dev/null

timeDesign -postCTS -pathReports -drvReports -slackReports -numPaths 50 -prefix simple_spi_postCTS -outDir timingReports

#On-Chip

setAnalysisMode -cppr none -clockGatingCheck true -timeBorrowing true -useOutputPinCap true -sequentialConstProp false -timingSelfLoopsNoSkew false -enableMultipleDriveNet true -clkSrcPath true -warn true -usefulSkew true -analysisType onChipVariation -log true

#Route

setNanoRouteMode -quiet -routeWithTimingDriven false

setNanoRouteMode -quiet -routeWithSiDriven false

routeDesign -globalDetail

#PostRoute ECO

setOptMode -fixCap true -fixTran true -fixFanoutLoad false

setDelayCalMode -engine default -siAware true

optDesign -postRoute

#PostRoute Report

redirect -quiet {set honorDomain [getAnalysisMode -honorClockDomains]} > /dev/null

timeDesign -postRoute -pathReports -drvReports -slackReports -numPaths 50 -prefix simple_spi_postRoute -outDir timingReports

#Filler

getFillerMode -quiet

addFiller -cell FILL64 FILL32 FILL16 FILL8 FILL4 FILL2 FILL1 -prefix FILLER

#Verify

getMultiCpuUsage -localCpu

get_verify_drc_mode -disable_rules -quiet

get_verify_drc_mode -quiet -area

get_verify_drc_mode -quiet -layer_range

get_verify_drc_mode -check_ndr_spacing -quiet

get_verify_drc_mode -check_only -quiet

get_verify_drc_mode -check_same_via_cell -quiet

get_verify_drc_mode -exclude_pg_net -quiet

get_verify_drc_mode -ignore_trial_route -quiet

get_verify_drc_mode -max_wrong_way_halo -quiet

get_verify_drc_mode -use_min_spacing_on_block_obs -quiet

get_verify_drc_mode -limit -quiet

set_verify_drc_mode -disable_rules {} -check_ndr_spacing auto -check_only default -check_same_via_cell true -exclude_pg_net false -ignore_trial_route false -ignore_cell_blockage false -use_min_spacing_on_block_obs auto -report simple_spi.drc.rpt -limit 1000

verify_drc

set_verify_drc_mode -area {0 0 0 0}

#Sdf File

setLayerPreference violation -isVisible 1

violationBrowser -all -no_display_false -displayByLayer

all_hold_analysis_views

all_setup_analysis_views

write_sdf -ideal_clock_network simple_spi.sdf

#Netlist File

violationBrowser -all -no_display_false -displayByLayer

win

violationBrowserClose

saveNetlist simple_spi.v스크립트 파일의 각 단계는 #을 통해 구분지어 놨고 GUI를 통해 설정하는 과정과 동일한 과정을 수행하게 된다.

위와 같이 스크립트 파일이 완성되면 innovus의 스크립트 파일 실행 명령어를 통해 실행한다.

innovus -files [스크립트 파일]

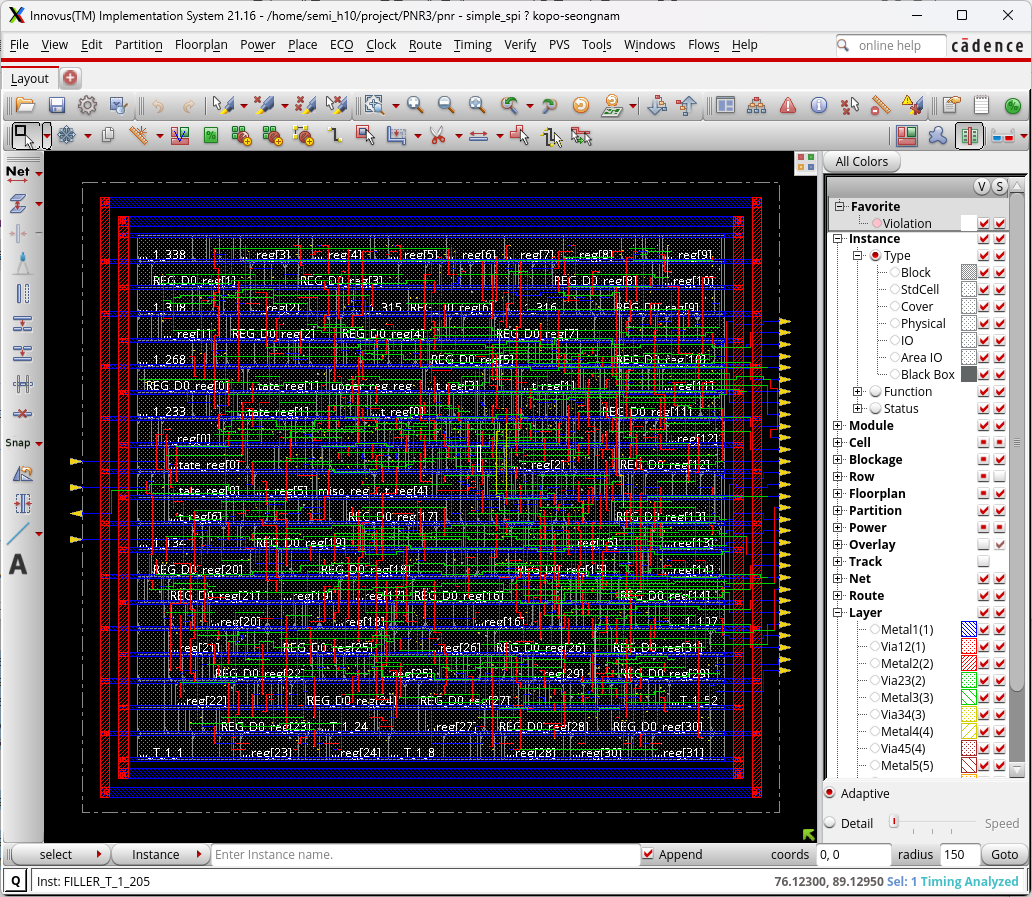

스크립트 파일을 정상적으로 작성했다면 GUI를 통해 Verify를 통해 DRC 체크를 했을 때와 동일한 0 Viols를 확인할 수 있으며, 위와 같이 완성된 P&R 화면을 확인할 수 있다.

'반도체 Study > 디지털 설계' 카테고리의 다른 글

| Verilog - CHARACTER LCD에 문자 입력하기 (0) | 2024.06.18 |

|---|---|

| Verilog- FPGA를 이용한 DC 모터 구동 (0) | 2024.06.11 |

| Innovus - P&R (SETUP ~ GDSII) (0) | 2024.06.05 |

| Verilog - SPI (Master, Slave, FSM) (2) FSM, MASTER, SLAVE & SLVAE 활용 (0) | 2024.06.02 |

| Verilog - SPI (Master, Slave, FSM) (1) FSM, SLAVE (0) | 2024.06.02 |