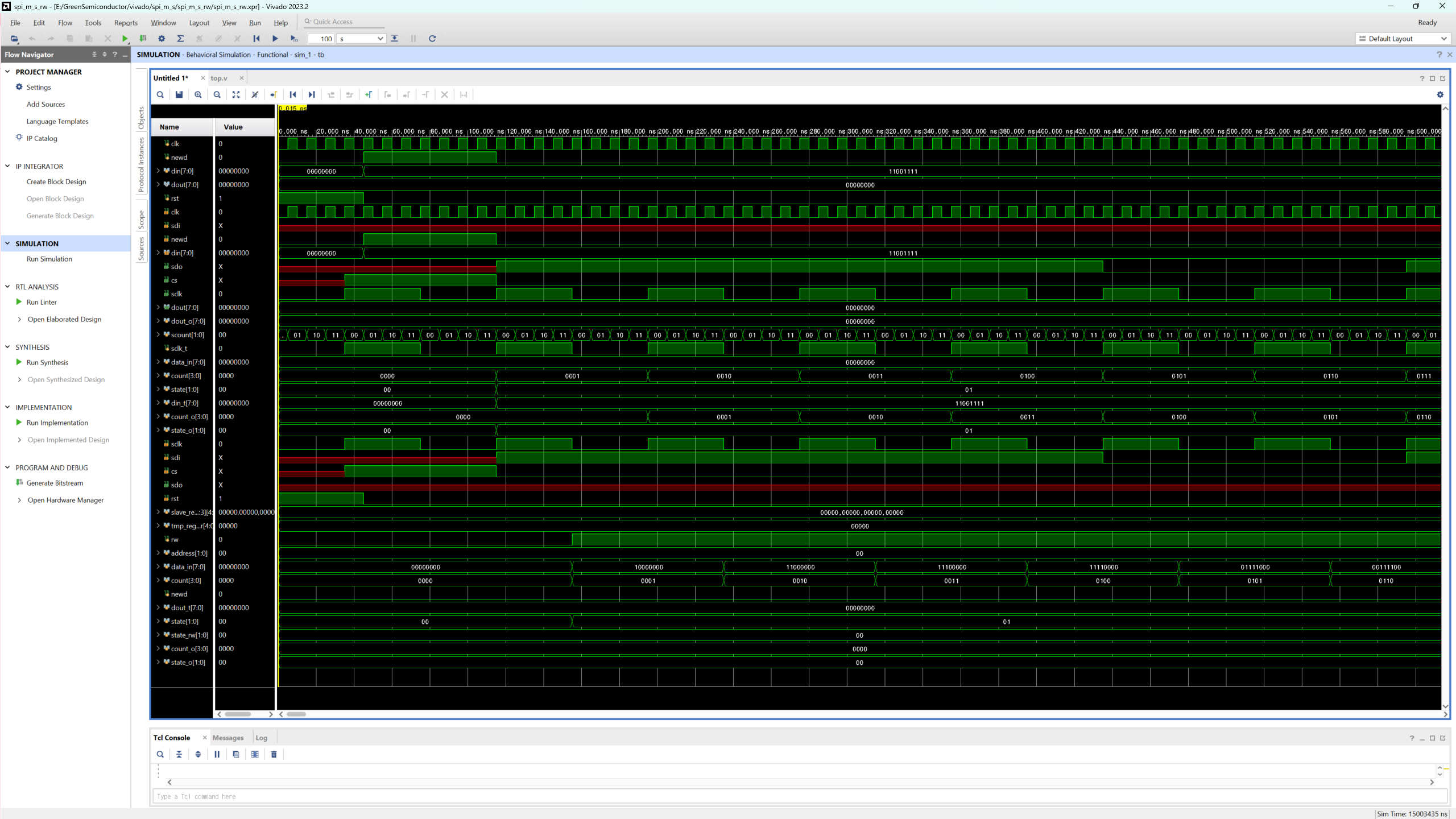

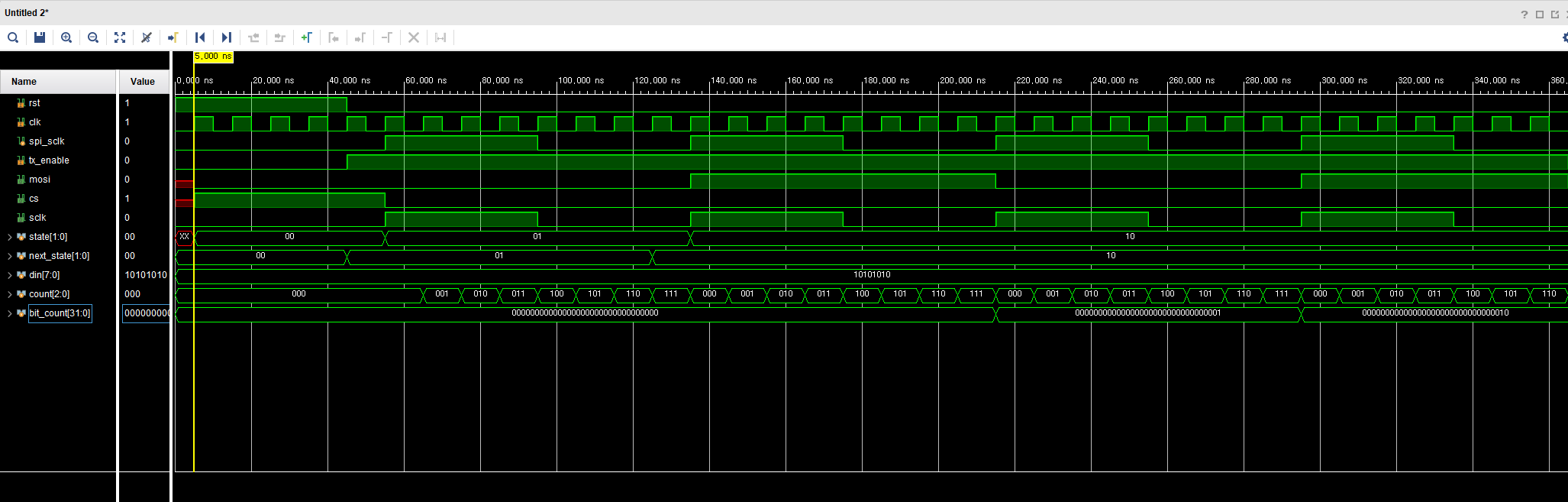

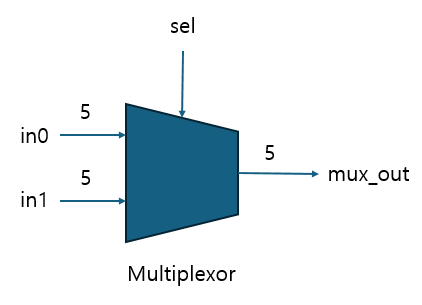

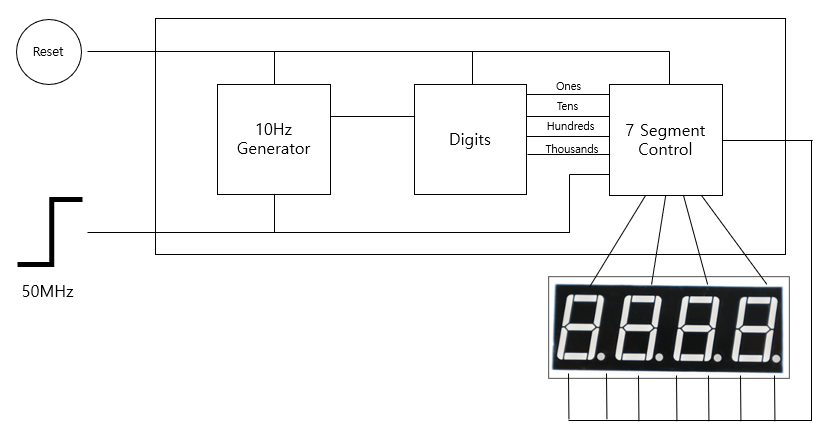

https://insoobaik.tistory.com/571 SPI - Serial Peripheral Interface 통신보호되어 있는 글입니다. 내용을 보시려면 비밀번호를 입력하세요.insoobaik.tistory.comSPI 이론과 관련된 내용은 위 글을 참조한다.SPI Slave (FPGA)Slave로 들어오는 bit는 총 32bit가 들어오게 된다.0~1 bit : ID 값 전달 bit2 bit : READ/WRITE 값 전달 bit (0 READ / 1 WRITE)3 bit : ADDRESS 값 전달 bit (현재 간단한 통신 테스트를 위해 2개의 16bit Register를 사용하는 예시에 해당하며, 0일경우 0번 Register, 1일경우 1번 Register에 접근4~15 bit : ..