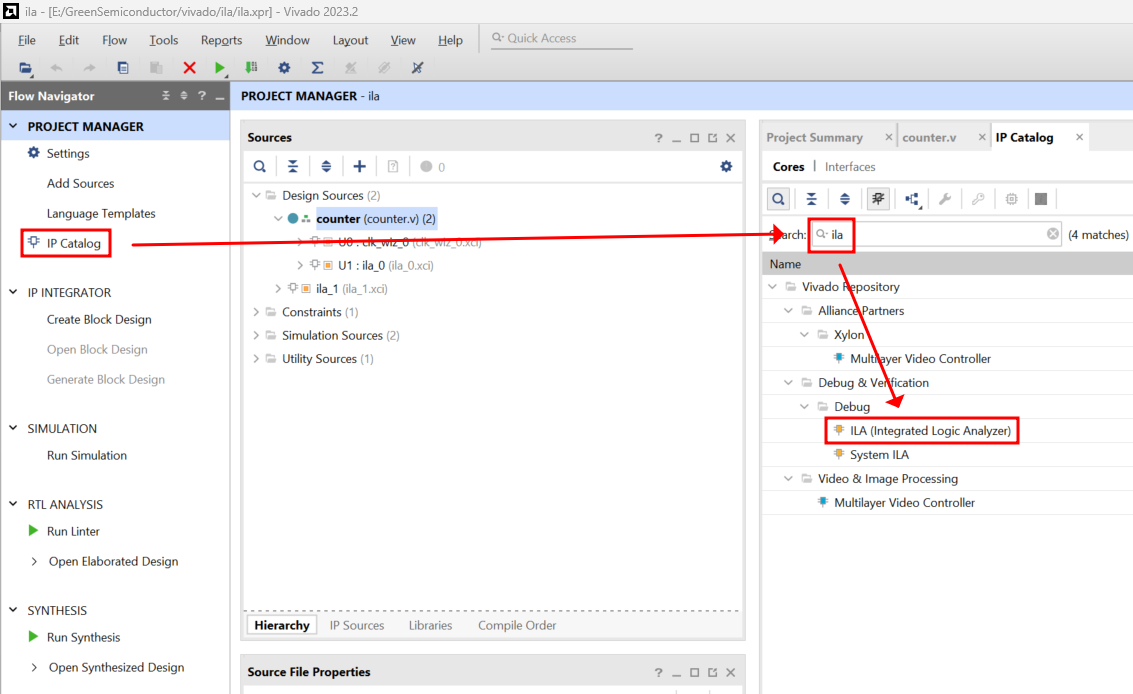

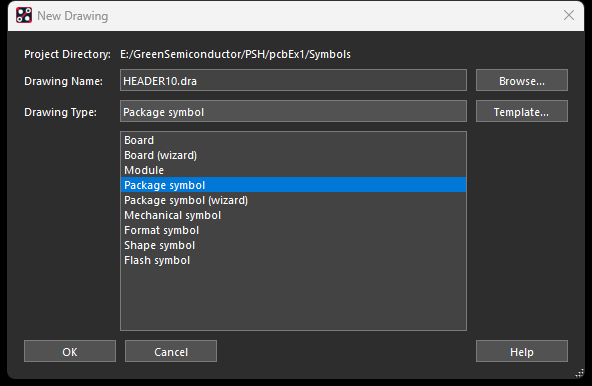

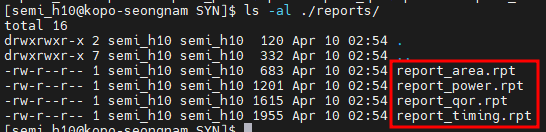

ILA(Integrated Logic Analyzer)는 디지털 회로의 디버깅과 분석을 위해 사용되는 도구이다. FPGA(Flexible Programmable Gate Array) 디자인에서 유용하다. ILA는 디지털 회로의 내부 신호를 모니터링하고 분석하는 데 도움이 되며, 디버깅 시간을 단축하고 회로의 동작을 이해하는데 도움이 된다. 좌측 IP Catalog를 클릭하여 검색창에 ila를 검색한다. Number of probes는 ILA로 캡처하려는 시그널의 수를 지정하는 항목이다. 이 값은 ILA에서 감시하고 분석할 수 있는 시그널의 개수를 결정한다.일반적으로 디버깅할 시그널의 수가 많을수록 문제 해결이 더욱 쉬워지지만, FPGA 디바이스의 리소스가 한정되어 있기 때문에 최적의 수를 지정해야 한다...