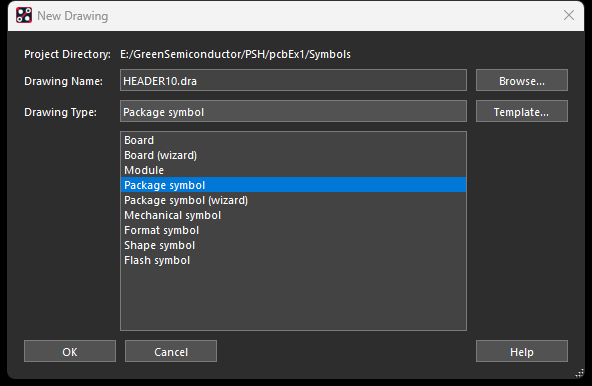

※ 작업경로(C:\SPB_Data)에 폴더명을 Symbols로 입력해야 직접 만든 라이브러리를 인식할 수 있다. - J1 커넥터 (HEADER 10) 조건에 맞게 수정 후 Update to Design을 통해 update 해준다. 선의 조건을 입력하고 조건에 맞게 그려준다. Command : x –3.1 5.08 ▶ ix 8.75 ▶ iy –20.32 ▶ ix –8.75 ▶ iy 20.32 Package Geometry : Assembly TOP, Silkscreen TOP에 대하여 외각선을 그려준다. Silkscreen_Top으로 위 부분도 생성해준다. * 문제에 외각선에 대한 정보가 주어지지 않으면 눈짐작으로 그리면 된다. - 조립을 위한 참조번호 입력하기 * Footprint 영역은 Place_Bo..