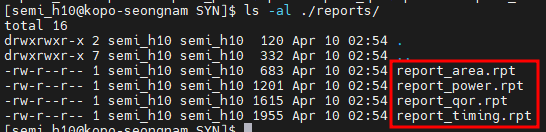

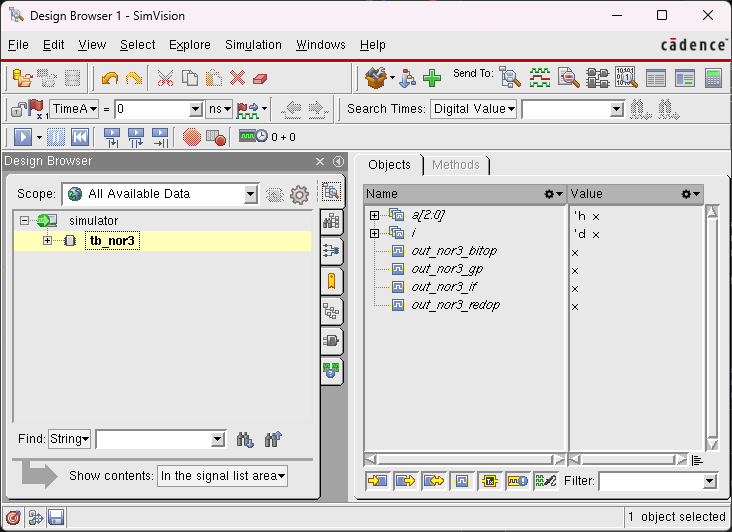

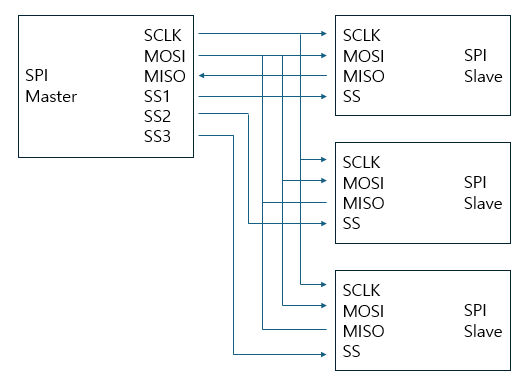

SynthesisSynthesis(합성)는 고수준의 HDL 코드를 하드웨어 리소스로 변환하여 구현 가능한 하드웨어로 만드는 작업이다. 합성을 하기 위해서는 게이트에 대한 정보(delay 등)를 담고 있는 [.lib 파일], 코드로 작성한 디지털 회로 설계 파일 [.v 파일], CLK 정보를 담고 있는 [.sdc] 파일이 필요하다. run_counter.tclset_db init_lib_search_path ../../LIB/ // 라이브러리 파일 위치set_db init_hdl_search_path ./rtl/ // hdl 파일 경로read_libs slow_vdd1v0_basicCells.lib // lib 파일명read_hdl counter.v // hdl 파일명elaborateread_s..