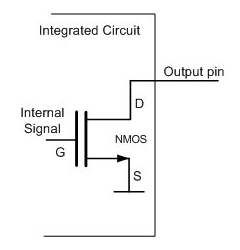

I2C에 대해 알아보기 전에 Open Drain이란 개념이 등장하기 Open Drain에 대해 간단하게 알아보겠다. - I2C에서 Open Drain을 사용하는 이유I2C는 여러 장치가 동일한 선을 공유하는 방식이다. Open Drain 방식을 사용하면 하나의 선에 여러 장치가 데이터를 공유할 수 있기 때문이다. 또 신호 충돌을 방지할 수 있기 때문이다. 자세한 내용은 아래를 참고하길 바란다. ■ Open Drain Open Drain은 위 그림과 같이 Drain이 Output Pin에 연결된 구조를 의미한다.위와 같이 Pull-Up 저항이 없게 되면 Floating 상태가 되어 신호가 불안정해지고 잡음의 영향을 받을 수 있다.위와 같이 Pull-Up 저항을 사용하게 되면 Data 선에 1의 신호를 지속..